The Solid State Imaging Technology

EZAVERIGANIKA

A Schlümberger Company

During the '70s, Fairchild led the development of CCD Technology. Since the beginning, the buried-channel concept has been utilized in all CCD products. The product line therefore exhibits all the advantages of buried-channel technology including low noise, high speed and high density.

Transferring this process from an R & D operation to a volume production environment required extensive efforts in research, design, development and production engineering. Our efforts paid off. Fairchild leads the way in CCD technology.

Fairchild CCD Imaging offers a broad product line. Specifically, we offer line scan sensors with 256 to 3,456 elements of resolution. We carry a full line of both line scan and area cameras. In addition we have a new line of vision interface processors. We also offer signal processing devices including video delay lines.

The '80s is the CCD Decade. And Fairchild is the CCD Leader.

# **TABLE OF CONTENTS**

| I.   | INTRODUCTION                                             | 3   |

|------|----------------------------------------------------------|-----|

| II.  | LINE SCAN SENSORS AND BOARDS                             | _   |

|      | CCD111                                                   |     |

|      | I-SCAN Design Development Set                            |     |

|      | CCD112                                                   |     |

|      | CCD122                                                   |     |

|      | CCD122 Design Development Board                          |     |

|      | CCD123                                                   |     |

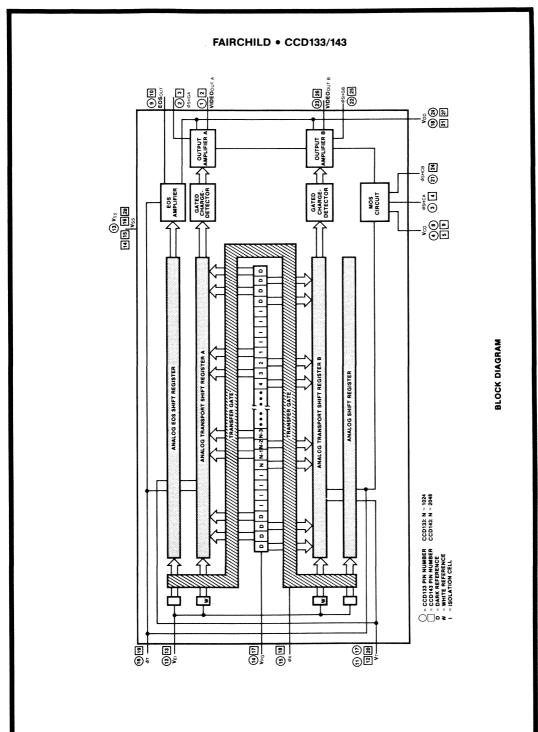

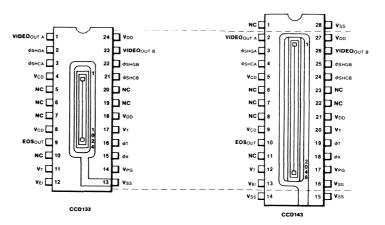

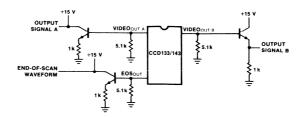

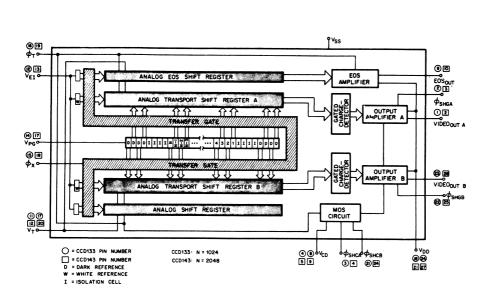

|      | CCD133/143                                               |     |

|      | CCD133A Technical Update                                 |     |

|      | CCD143A Technical Update                                 |     |

|      | CCD133/143 Design Development Board                      |     |

|      | CCD133K Color Sensor                                     |     |

|      | CCD134                                                   |     |

|      | CCD145                                                   |     |

|      | CCD151                                                   |     |

|      | CCD 151 Design Development Board                         | 98  |

| III. | SIGNAL PROCESSING DEVICES AND MODULES                    |     |

|      | Signal Processing Products Summary                       | 103 |

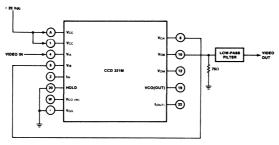

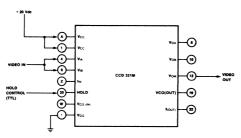

|      | CCD321A                                                  | 105 |

|      | CCD321M                                                  | 113 |

|      | CCD323A                                                  | 119 |

| IV.  | CAMERAS AND ACCESSORIES                                  |     |

|      | Commercial Line Scan Camera Summary                      | 128 |

|      | Commercial Line Scan Cameras CCD1100/1300                | 129 |

|      | CCD1200/1500 Commercial Line Scan Cameras                |     |

|      | Pixel Locator                                            | 143 |

|      | CCD1000 Industrial Line Scan Camera Series               |     |

|      | Industrial Line Scan Cameras CCD1200/1300/1500           | 145 |

|      | CCD3000 Automation Camera Series                         |     |

|      | CCD3000 Basic Automation Camera                          | 149 |

|      | CCD3000F Fiber Optic Camera                              |     |

|      | CCD3001 Element Anti-blooming Camera                     |     |

|      | CCD3001F Fiber Optic Camera                              |     |

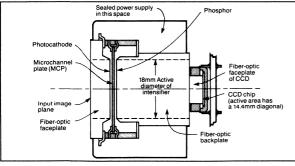

|      | CCD3001I Intensified Camera                              |     |

|      | CCD4001 Robotics Camera                                  |     |

| V.   | VISION INTERFACE PROCESSORS                              |     |

| V.   | VIP100 Vision Interface Processor                        | 167 |

|      | VIF100 VISION INTERIACE FIOCESSOI                        | 107 |

| VI.  | ARTICLES AND GRAPHS                                      |     |

|      | CCD Fundamentals                                         |     |

|      | Charge Coupled Device Principles                         |     |

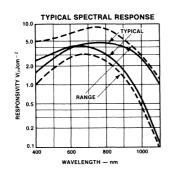

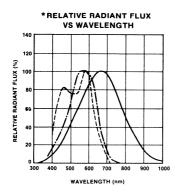

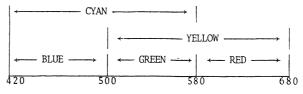

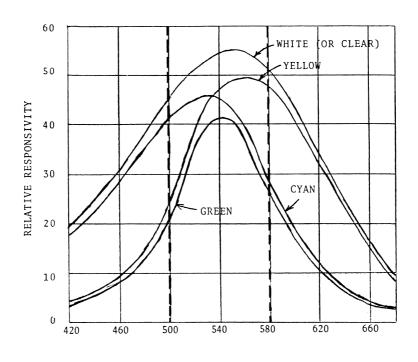

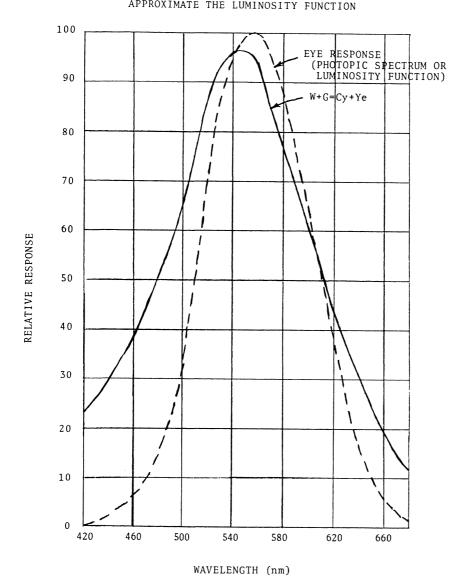

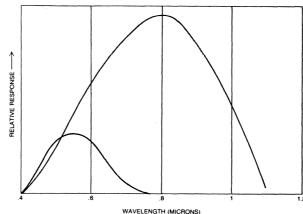

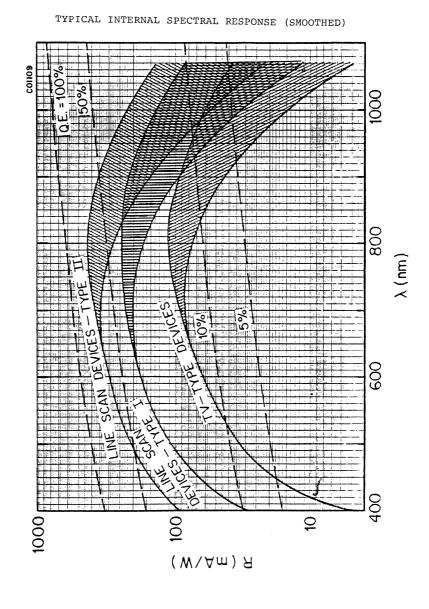

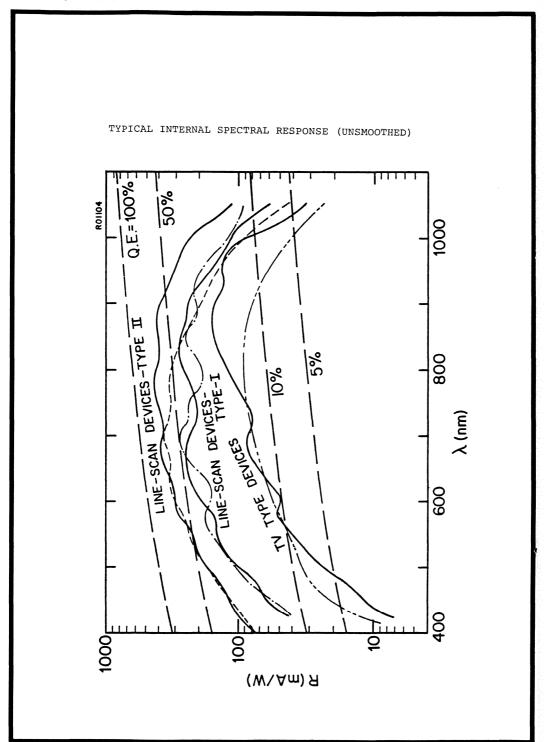

|      | Spectral Response Curves                                 |     |

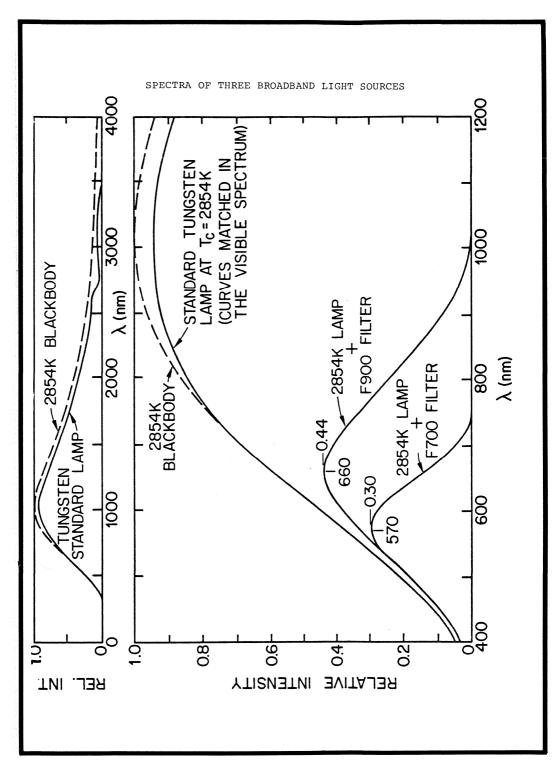

|      | Illumination Source Spectra                              | 187 |

|      | Technical Note on X-Ray Imaging                          | 188 |

|      | Note on CCD Line Imaging Devices                         |     |

|      | Technical Note on the Effects of Irradiance              |     |

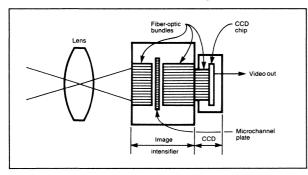

|      | Intensified CCD Camera Uses Fiber Optic Coupling         | 200 |

|      | Vision Interface Processor Links CCD Cameras to Multibus |     |

|      | Technical Insights                                       | 206 |

# INTRODUCTION

#### **Line Scan Image Sensors**

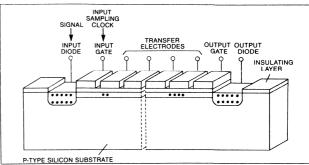

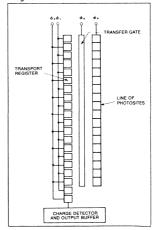

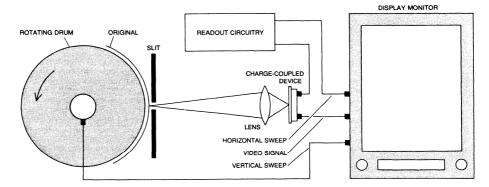

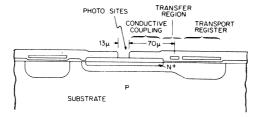

Basically, a line scan image sensor is composed of a row of image sensing elements (photosites), two analog transport registers, and an output amplifier. Light energy falls on the photosites and generates charge packets proportional to the light intensity. These charge packets are then transferred in parallel to two analog transport registers, which are clocked by 2-phase clocks. The packets are next delivered to an on-chip output amplifier where they are converted to proportional voltage levels. A series of pulses, amplitude modulated with the optical information, appear at the output.

Key advantages of Fairchild CCD line scan sensors, due to Fairchild's

Isoplanar buried-channel structure, include high data rates, high charge transfer efficiencies, low noise, and relatively small die sizes.

Line scan sensors find applications ranging from optical character recognition (OCR) using the 256×1 device to facsimile sensing using the 1728×1 or 3456×1 device. The precise location of the photosites on the sensor allows the device to be used in high precision non-contact measurement applications such as dimensional measurements of objects, shape recognition and sorting, and defect detection.

The following tables summarize the features of Fairchild's Line Scan Imaging Products.

#### Line Scan Sensor

| Order<br>Code | Number of<br>Elements | Element<br>Size | Maximum<br>Data Rate | Range<br>(Typical) | Responsivity<br>(Typical) |

|---------------|-----------------------|-----------------|----------------------|--------------------|---------------------------|

| CD111ADC      | 256×1                 | 13×17 microns   | 10 MHz               | 2500:1             | 1.3 V per µj/cm²          |

| CD111BDC      | 256×1                 | 13×17 microns   | 10 MHz               | 2500:1             | 1.1 V per µj/cm²          |

| CCD112DC      | 256×1                 | 13×13 microns   | 5 MHz                | 5000:1             | 3.0 V per µj/cm²          |

| CCD133DC      | 1024×1                | 13×13 microns   | 20 MHz               | 5000:1             | 3.0 V per µj/cm²          |

| CCD134DC      | 1024×1                | 13×13 microns   | 20 MHz               | 5000:1             | 3.0 V per µj/cm²          |

| CCD122DC      | 1728×1                | 13×13 microns   | 2 MHz                | 2500:1             | 3.5 V per μj/cm²          |

| CCD123DC      | 1728×1                | 10×13 microns   | 2 MHz                | 2500:1             | 3.5 V per µj/cm²          |

| CCD143DC      | 2048×1                | 13×13 microns   | 20 MHz               | 5000:1             | 3.0 V per µj/cm²          |

| CCD145DC      | 2048×1                | 13×13 microns   | 8 MHz                | 2500:1             | 4.0 V per µj/cm²          |

| CCD151DC      | 3456×1                | 7×7 microns     | 5 MHz                | 2500:1             | 4.0 V per μj/cm²          |

#### Line Scan Design Aids (do not include sensors)

| Order<br>Code                               | Sensor<br>Supported                                      | Comments                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I-SCAN* CCD133DB CCD122DB CCD143DB CCD151DB | CD111ADC<br>CCD133DC<br>CCD122DC<br>CCD143DC<br>CCD151DC | Fairchild offers a series of printed circuit boards for use as construction aids for experimental systems using CCD line scan image sensors. These design and development boards are fully assembled and tested, and require only power supplies and an oscilloscope to display the video information corresponding to the image positioned in front of the sensor. |

<sup>\*</sup>I-SCAN includes CD111ADC

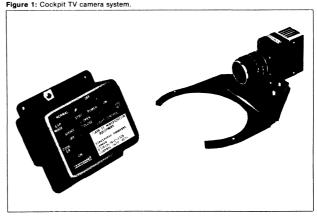

#### Camera Subsystems

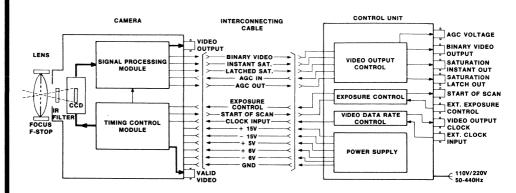

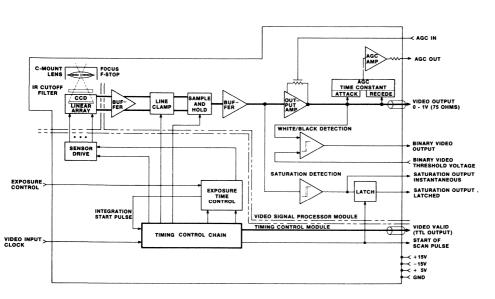

Fairchild CCD camera subsystems are fully assembled and calibrated electro-optical instruments useful in a wide variety of scientific and industrial applications.

Each subsystem is comprised of a camera, a line-powered control unit, and interconnecting cables. The camera, which may be ordered separately, may be equipped with a lens suitable for the application.

Line Scan Camera resolutions of 256, 512, 1024 and 2048 elements per line are available. Line scan subsystems are particularly useful for acquisition of optical data for objects in motion, i.e., facsimile scanning of documents transported past the camera's field of view or measurement of objects carried past a camera inspection station on a conveyor belt. Typical subsystem applications include microfiche and microfilm scanning, document scanning for mark sensing, facsimile transduction and OCR data acquisition; precision non-contact measurement and inspection, flaw detection, shape

analysis, dimensional measurement, color sorting; and for a wide variety of laboratory uses.

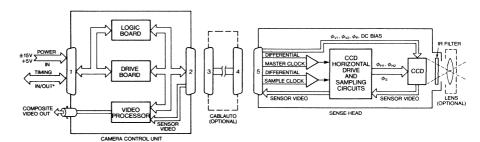

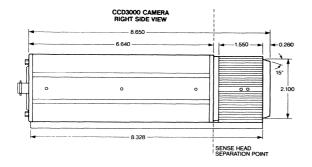

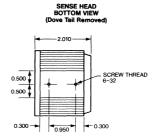

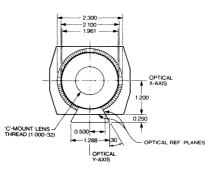

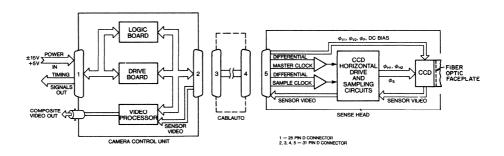

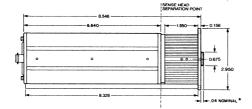

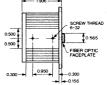

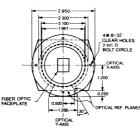

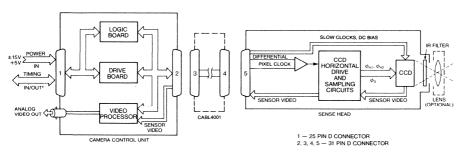

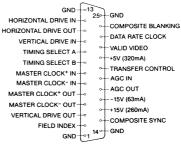

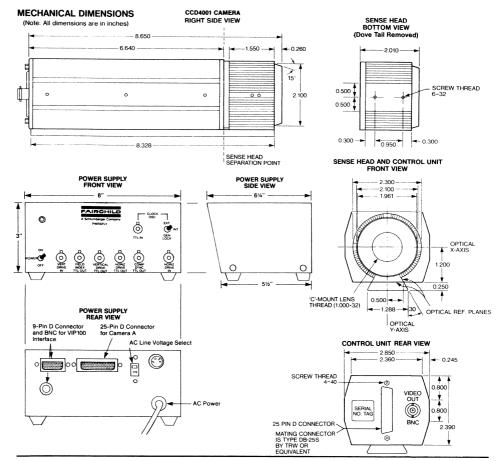

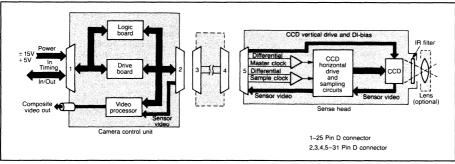

Area Cameras are ideally suited for industrial environments. The CCD3000 Video Communications Camera provides standard television output signals for display of highresolution images on low-cost monitors or for digital analysis using NTSC image processing equipment. The CCD3000 is also available with a fiber optic faceplate for interfacing to customer fiber optic image inputs as well as with an image intensifier for low light level applications. The CCD4001 Robotics Camera provides image data output in a non-interlaced 256 by 256 element square pixel pitch format which can be utilized by a CPU for automatic inspection, recognition and robot guidance. All Fairchild area cameras can be used as a relatively small single-component camera, or be separated into a camera control unit plus a cable-connected sense head which is robust enough to be mounted onto a robot arm.

100 KHz - 10 MHz

#### Commercial Line Scan Camera System

CCD1500C

Includes Camera Control Unit and Interconnect Cables Camera only may be ordered as CAM1100C, CAM1200C, CAM1300C, CAM1400C or CAM1500C.

| Order<br>Code | Number of<br>Elements | Line Scan<br>Rate | Exposure<br>Time | Data<br>Rate     |

|---------------|-----------------------|-------------------|------------------|------------------|

| CCD1100C      | 256×1                 | 60 Hz - 35 KHz    | 30 µs - 16 ms    | 100 KHz - 10 MHz |

| CCD1200C      | 512×1                 | 60 Hz - 20 KHz    | 51 µs - 16 ms    | 100 KHz - 10 MHz |

| CCD1300C      | 1024×1                | 60 Hz - 10 KHz    | 102 µs - 16 ms   | 100 KHz - 10 MHz |

| CCD1400C*     | 1728×1                | 60 Hz - 6 KHz     | 175 µs - 16 ms   | 100 KHz - 10 MHz |

204 µs - 16 ms

#### Industrial Line Scan Camera System (camera only)

2048×1

| Order    | Number of | Max. Line       | Min. Exposure | Data             |

|----------|-----------|-----------------|---------------|------------------|

| Code     | Elements  | Scan Rate       | Time          | Rate             |

| CCD1200R | 512×1     | 38 K lines/sec  | 26 μs         | 100 KHz - 20 MHz |

| CCD1300R | 1024×1    | 19 K lines/sec  | 52 μs         | 100 KHz - 20 MHz |

| CCD1500R | 2048×1    | 9.7 K lines/sec | 103 μs        | 100 KHz - 20 MHz |

<sup>60</sup> Hz - 5 KHz \*The CCD1400C and CAM1400C are being discontinued. Stock is currently available in small quantities.

#### Area Camera Systems

Includes Camera, Power Supply and Remote Sense Head Cable.

Camera only may be ordered as CAM3000, CAM3100, CAM3000F, CAM3100F or CAM4001.

| Order<br>Code | Scanning format              | Comment                        |

|---------------|------------------------------|--------------------------------|

| CCD3000       | Full 488×380 NTSC Resolution |                                |

| CCD3100       | Full 488×380 NTSC Resolution | 222A Sensor                    |

| CD3000F       | Full 488×380 NTSC Resolution | Fiber Optic Faceplate          |

| CCD3100F      | Full 488×380 NTSC Resolution | 222A and Fiber Optic Faceplate |

| CCD4001       | 256×256 Non-Interlaced       |                                |

#### Camera Accessories

| Order<br>Code | For use with           | Description                           |

|---------------|------------------------|---------------------------------------|

| LENS13C       | All (except CCD1500)   | 13 mm Lens, Standard C Mount          |

| LENS25C       | All (except CCD1500)   | 25 mm Lens, Standard C Mount          |

| LENS50C       | All (except CCD1500)   | 50 mm Lens, Standard C Mount          |

| LENS28B       | CCD1500C, CCD1500R     | 28 mm Lens, Bayonet Mount             |

| LENS50B       | CCD1500C, CCD1500R     | 50 mm Lens, Bayonet Mount             |

| CNTRLINE      | Comm. Line Scan Camera | Control Unit with Interconnect Cables |

| CABLE         | Comm. Line Scan Camera | Interconnect Cables only              |

| CABLAUTO      | CCD3000, CCD3000F      | Remote Sense Head Cable for CCD3000   |

| CABL4001      | CCD4001                | Remote Sense Head Cable for CCD4001   |

| PWRSPLY       | CCD3000                | Power Supply                          |

| PIX1100       | CCD1100C               | Pixel Locator                         |

| PIX1200       | CCD1200C               | Pixel Locator                         |

| PIX1300       | CCD1300C               | Pixel Locator                         |

| PIX1400       | CCD1400C               | Pixel Locator                         |

| PIX1500       | CCD1500C               | Pixel Locator                         |

| MONITOR       | CCD3000, CCD4001       | NTSC Monitor, Black and White         |

#### **Vision Interface Processor**

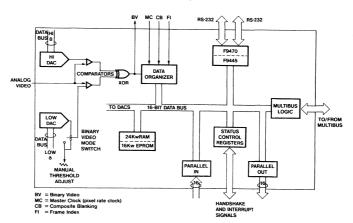

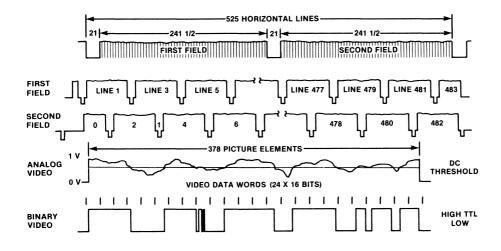

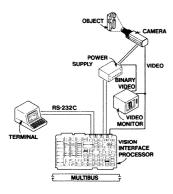

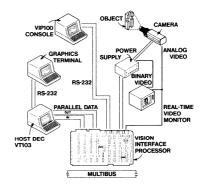

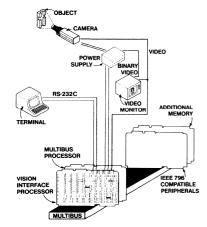

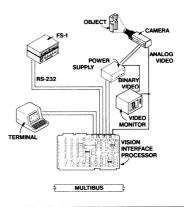

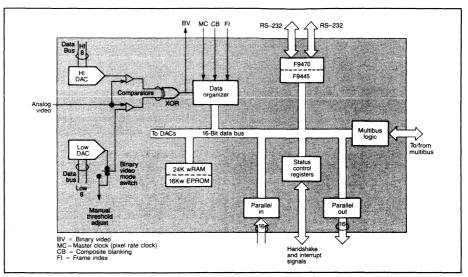

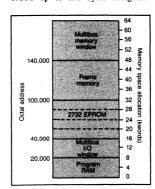

In many applications there is a need for decision-making based on the data from CCD cameras rather than just for a display of imagery. To yield a decision, the camera data must first be converted from analog to digital and subsequently interpreted. Fairchild's multibus\* formatted VIP100 Vision Interface Processor accepts analog video from any Fairchild CCD camera. It converts the analog video to binary and then processes the converted data, which enables it to perform a host of industrial inspection and robotic vision system functions. Processing is accomplished using

the on-board 16-bit 20MHz Fairchild F9445 microprocessor. Applications include Non-Contact Measurement, Defect, Surface Flaw and Edge Flaw Detection, Automated Parts sorting, OCR, Shape and Pattern Recognition, Object Recognition and Robot Guidance.

This versatile board is capable of being used as a stand alone processor or as part of a larger system using the link to the multibus, either of two RS-232 ports or separate user configurable 16-bit data input and output ports.

#### Computer Interface Systems

| Order<br>Code | For use with          | Description                             |

|---------------|-----------------------|-----------------------------------------|

| VIP100-20     | All Fairchild cameras | Vision Interface Card with 20 MHz F9445 |

<sup>\*</sup> Multibus is a trademark of Intel Corporation.

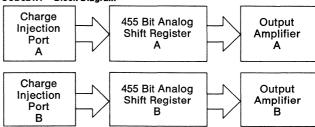

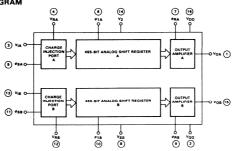

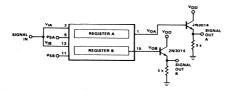

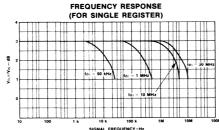

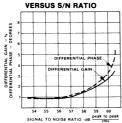

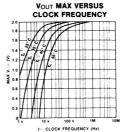

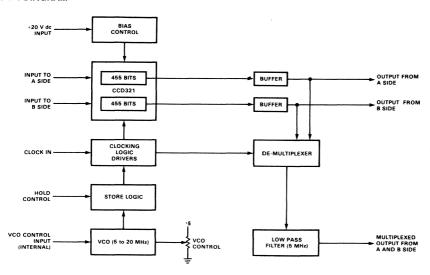

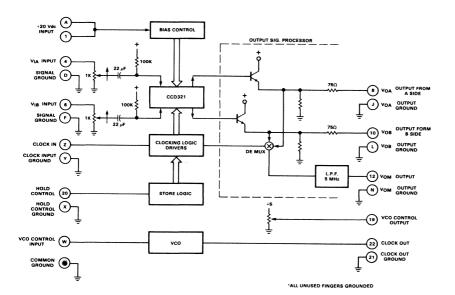

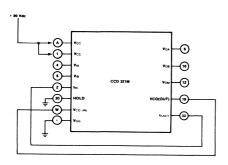

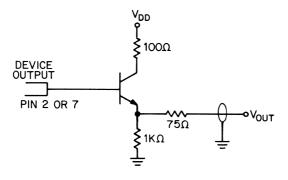

### **Signal Processing**

The capability to manipulate information in the form of discrete charge packets makes CCD technology ideal for analog signal processing. Fairchild signal processing components are monolithic silicon structures comprised of CCD analog shift registers, charge injection ports, and output charge-sensing amplifiers. They can be advantageously used for delay and temporary storage of analog video signals. The time delay for data transit through the CCD register is precisely controlled by the frequency of the externally supplied transport clock signal. Fairchild signal processing components include a sample-and-hold signal output stage for ease of application.

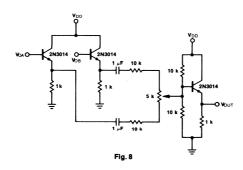

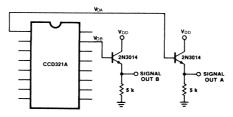

Fairchild video delay modules are printed circuit board structures which include the CCD321A3 device and are sold as fully assembled and calibrated units. The module is equipped for use as a variable delay circuit, using either an externally supplied or internal variable frequency clock, or for temporary analog data storage in a stopped-clock mode.

Typical applications for the CCD signal processing components and modules include time base correction for video tape recorders, fast input-slow output data expansion systems for A-D converter systems, comb filter realizations, drop-out compensators, and other analog applications up to frequencies of 30 MHz data rate.

#### Signal Processing Products

| Order<br>Code | Description                                |

|---------------|--------------------------------------------|

| CCD321A1      | NTSC Broadcast Quality Video Delay Line    |

| CCD321A2      | NTSC Industrial Quality Video Delay Line   |

| CCD321A3      | NTSC Time Base Correction Video Delay Line |

| CCD321VM      | Video Delay Module (includes the CCD321A3) |

| CCD323A       | PAL Video Delay Line                       |

For further information on Fairchild CCD Imaging and Signal Processing products, call your nearest Fairchild Sales Office, representative, or distributor.

For technical or applications information and assistance, call (415) 493-8001, (TWX 910-373-2110) or write Fairchild CCD Imaging, 3440 Hillview Avenue, Palo Alto, California 94304.

Sensors

# **CCD 111** 256-Element Line Scan Image Sensor

**CCD Imaging**

#### Description

The CCD111 is a monolithic 256-element line image sensor. The device is designed for optical character recognition and other imaging applications that require high sensitivity and high speed. The CCD111 is pin-for-pin compatible with and a functional replacement for the CCD110F.

In addition to a line of 256 sensing elements, the CCD111 chip includes: two charge transfer gates, two 2-phase analog transport shift registers, an output charge detector/amplifier, and a compensation amplifier. The transport registers both feed the input of the charge detector resulting in sequential reading of the 256 sensing

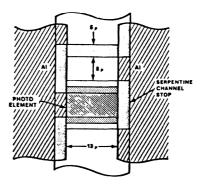

The cell size is 13  $\mu$ m (0.51 mils) by 17  $\mu$ m (0.67 mils) on 13 µm (0.51 mils) centers. The device is manufactured using Fairchild advanced charge-coupled device n-channel Isoplanar buried-channel technology.

- **DYNAMIC RANGE TYPICAL: 2500:1**

- ON-CHIP VIDEO AND COMPENSATION AMPLIFIERS

- LOW POWER REQUIREMENTS

- **ALL OPERATING VOLTAGES 15V AND UNDER**

- LOW NOISE EQUIVALENT EXPOSURE

- DIMENSIONALLY PRECISE PHOTOSITE SPACING

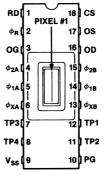

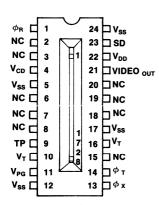

#### **Connection Diagram**

DIP (TOP VIEW)

### Pin Names:

| ru                                             | rnologale          |

|------------------------------------------------|--------------------|

| $\phi_{XA}$ , $\phi_{XB}$                      | Transfer Clock     |

| $\phi_{1A}, \phi_{2A} \\ \phi_{1B}, \phi_{2B}$ | Transport Clocks   |

| og "                                           | Output Gate        |

| os                                             | Output Source      |

| OD                                             | Output Drain       |

| CS                                             | Compensation       |

|                                                | Source             |

| $\phi_{R}$                                     | Reset Clock        |

| RD                                             | Reset Drain        |

| TP                                             | Test Point         |

| Vss                                            | Substrate (ground) |

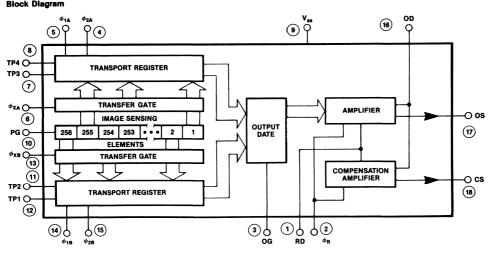

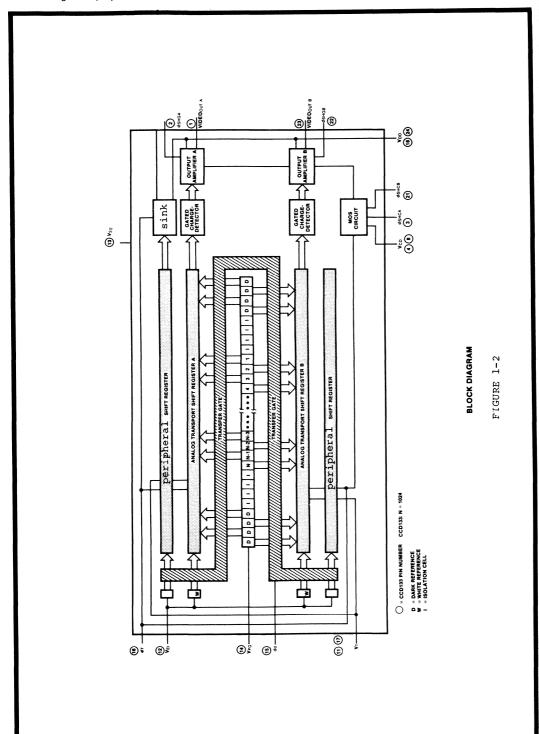

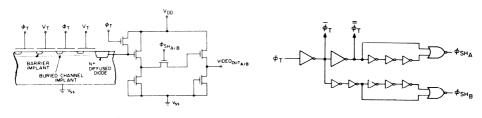

#### **Block Diagram**

#### **Functional Description**

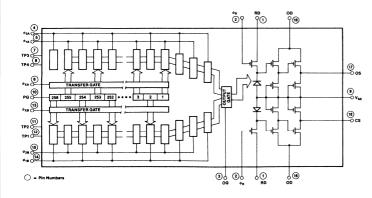

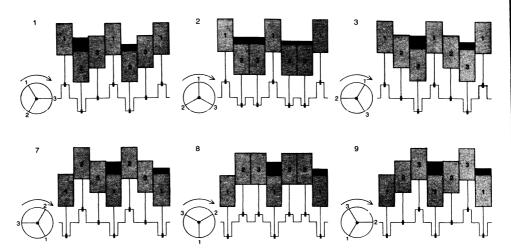

The CCD111 consists of the following functional elements illustrated in the Block Diagram:

Image Sensor Elements — A row of 256 Image sensor elements separated by a diffused channel stop and covered by a silicon photogate. Image photons pass through the transparent polycrystalline silicon photogate and are absorbed in the single crystal silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated background level at zero illumination to a maximum at saturation under bright illumination.

Two Transfer Gates — Gate structures adjacent to the row of image sensor elements. The charge packets accumulated in the image sensor elements are transferred out via the transfer gates to the transport registers whenever the transfer gate voltages go HIGH. Alternate charge packets are transferred to the left and right transport registers. The transfer gates also control the integration time for the sensing elements.

Two 130-Bit Analog Transport Shift Registers — One on each side of the line of image sensor elements and are separated from it by a transfer gate. The two registers, called the transport registers, are used to move the light generated charge packets delivered by the transfer gates serially to the charge detector/amplifier. The complementary phase relationship of the last elements of the two transport registers provides for alternate delivery of charge packets to establish the original serial sequence of the line of video in the output circuit.

A Gated Charge Detector/Amplifier — Charge packets are transported to a precharged diode whose potential changes linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of the output n-channel MOS transistor producing a signal at the output OS. A reset transistor is driven by the reset clock  $\langle \phi_R \rangle$  and recharges the charge detector diode capacitance before the arrival of each new signal charge packet from the transport registers.

#### **Definition of Terms**

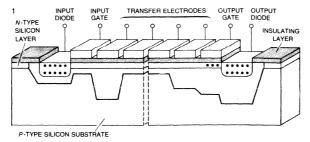

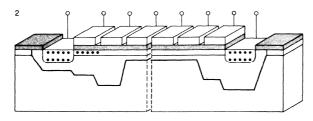

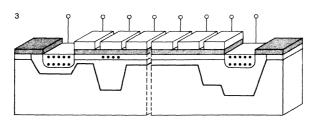

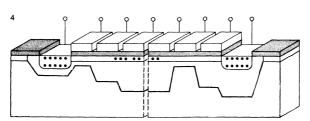

Charge-Coupled Device — A charge-coupled device is a semiconductor device in which finite isolated charge packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge packets

are minority carriers with respect to the semiconductor substrate.

Transfer Clocks  $\phi_{\chi A}$ ,  $\phi_{\chi B}$  — The voltage waveforms applied to the transfer gates to move the accumulated charge from the image sensor elements to the CCD transport registers.

Transport Clocks  $\phi_{1A}$ ,  $\phi_{2A}$ ,  $\phi_{1B}$ ,  $\phi_{2B}$  — The two sets of 2-phase waveforms applied to the gates of the transport registers to move the charge packets received from the image sensor elements to the gated charge detector/amplifier.

Gated Charge Detector/Amplifier — The output circuit of the CCD111 that receives the charge packets from the transport registers and provides a signal voltage proportional to the size of each charge packet received. Before each new charge packet is sensed, a reset clock returns the charge detector voltage to a fixed level.

**Reset Clock**  $\phi_R$  — The voltage waveform required to reset the voltage on the charge detector.

Dynamic Range — The saturation exposure divided by the rms noise equivalent exposure. (This does not take into account dark signal components.) Dynamic range is sometimes defined in terms of peak-to-peak noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times rms noise.

RMS Noise Equivalent Exposure — The exposure level that gives an output signal equal to the rms noise level at the output in the dark.

Saturation Exposure — The minimum exposure level that will produce a saturation output signal. Exposure is equal to the light intensity times the photosite integration time.

Charge Transfer Efficiency — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

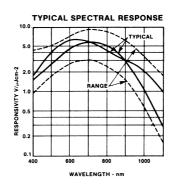

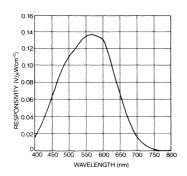

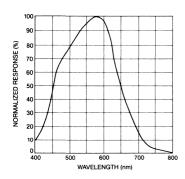

Spectral Response Range — The spectral band in which the response per unit of radiant power is more than 10% of the peak response.

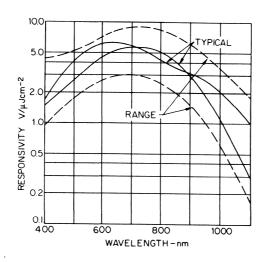

Responsivity — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure.

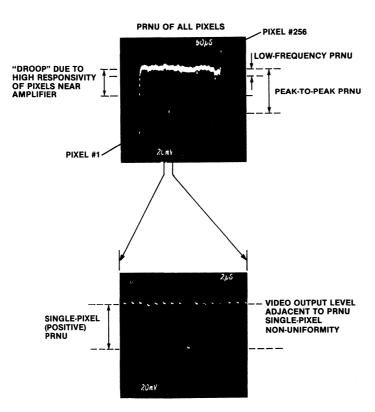

Total Photoresponse Non-uniformity — The difference of the response levels of the most and the least sensitive

element under uniform illumination. Measurement of PRNU excludes first and last elements. (See accompanying photos for details of definition.)

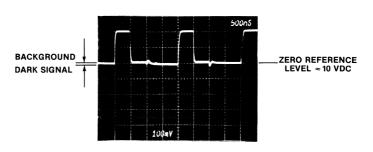

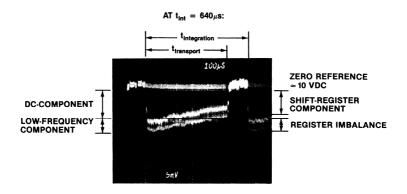

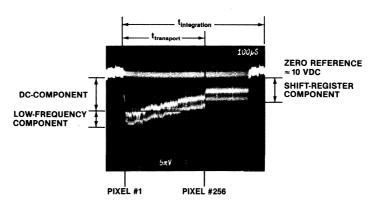

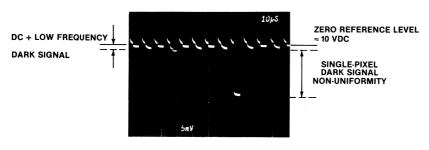

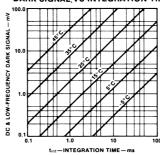

Dark Signal — The output signal in the dark caused by thermally generated electrons that is a linear function of the integration time and highly sensitive to temperature. (See accompanying photos for details of definition.)

Saturation Output Voltage — The maximum useable signal output voltage. Charge transfer efficiency decreases sharply when the saturation ouput voltage is exceeded.

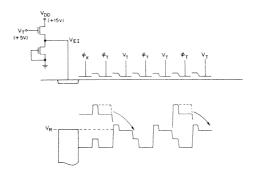

**Integration Time** — The time interval between the falling edges of any two transfer pulses  $\phi_{NB}$  or  $\phi_{NB}$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

Pixel - A picture element (photosite).

Peripheral Response — The output signal caused by light-generated charge that is collected by the transport registers (instead of the photosites). The device is covered, except over the photosites, by a gapped metal layer, which functions both as an array of interconnections and as a reflective light shield. The major component of Peripheral Response for visible light ( $\lambda \leq 700 \text{nm}$ ) is generated in the transport registers by light transmitted through these gaps in the metal above the registers. For near-infrared light ( $\lambda \geq 700 \text{nm}$ ), especially on CCD111A devices, a portion of the charge generated by light absorbed under the photosites and one transport register is collected in the opposite transport register.

Major Differences Between the CCD111A and CCD111B Both the CCD111A and the CCD111B have the same responsivity to visible light (400-700nm). The principal differences are as follows:

The CCD111A is intended for use in applications where very low dark signal and high responsivity to very near-infrared (700-900nm) light are needed, and where peripheral response is not critical.

The CCD111B is selected for use in applications where standard responsivity to very near-infrared (700-900nm) light and standard dark signal are acceptable and where peripheral response needs to be minimized.

It is not recommended that either part be used with illumination containing wavelengths greater than 900nm (near-infrared). If use of such a light source (unfiltered tungsten, for example) is unavoidable, the CCD111B will generally provide the user with more satisfactory results. The table on performance characteristics provides more information.

#### **Absolute Maximum Ratings**

| Storage Temperature        | - 25°C to 100°C            |

|----------------------------|----------------------------|

| Operating Temperature      | - 25°C to 55°C             |

| Pins 2, 3, 4, 5, 6, 7, 10, |                            |

| 12, 13, 14, 15             | - 0.3V to 15V              |

| Pins 1, 8, 11, 16          | -0.3V to 18V               |

| Pins 17, 18                | output, no voltage applied |

| Pin 9                      | ov                         |

|                            |                            |

#### **Caution Note**

This device has limited built-in gate protection. It is recommended that static discharge be controlled and minimized. Care must be taken to avoid shorting pins OS and CS to  $V_{SS}$  or  $V_{OD}$  during operation of the device. Shorting these pins temporarily to  $V_{SS}$  or  $V_{OD}$  may destroy the output amplifiers.

#### DC Characteristics: T<sub>c</sub> = 25°C (Note 1)

|                 | Limits                             |      |      |      |      |           |

|-----------------|------------------------------------|------|------|------|------|-----------|

| Symbol          | Characteristic                     | Min  | Тур  | Max  | Unit | Condition |

| V <sub>OD</sub> | Output Transistor<br>Drain Voltage | 14.5 | 15.0 | 15.5 | ٧    |           |

| $V_{RD}$        | Reset Transistor<br>Drain Voltage  | 11.5 | 12.0 | 12.5 | V    |           |

| $V_{OG}$        | Output Gate Voltage                | -    | 5.0  |      | v    |           |

| $V_{PG}$        | Photogate Voltage                  | 9.5  | 10.0 | 12.5 | V    |           |

| TP1, TP3        | Test Points                        |      | 0.0  |      | v    |           |

| TP2, TP4        | Test Points                        | 14.5 | 15.0 | 15.5 | v    |           |

Clock Characteristics:  $T_c = 25$ °C (Note 1)

|                                                                                                                           |                                                     |     | Limits |     |      |            |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|--------|-----|------|------------|

| Symbol                                                                                                                    | Characteristic                                      | Min | Тур    | Max | Unit | Condition  |

| $egin{aligned} \mathbf{V_{\phi1AL}}, \ \mathbf{V_{\phi1BL}} \ \mathbf{V_{\phi2AL}}, \ \mathbf{V_{\phi2BL}} \end{aligned}$ | Transport Clocks LOW                                | 0.0 | 0.5    | 0.8 | ٧    | Note 2     |

| $V_{\phi^1AH}^{},V_{\phi^1BH}^{},V_{\phi^2BH}^{}$                                                                         | Transport Clocks HIGH                               | 7.5 | 8.0    | 8.5 | v    | Note 5     |

| $V_{\phi XAL}$ , $V_{\phi XBL}$                                                                                           | Transfer Clock LOW                                  | 0.0 | 0.5    | 0.8 | v    | Notes 2, 5 |

| $V_{\phi XAH}, V_{\phi XBH}$                                                                                              | Transfer Clock HIGH                                 | 7.5 | 8.0    | 8.5 | v    | Note 5     |

| $V_{\phi RL}$                                                                                                             | Reset Clock LOW                                     | 0.0 | 0.5    | 0.8 | V    | Notes 2, 5 |

| $V_{\phi RH}$                                                                                                             | Reset Clock HIGH                                    | 7.5 | 8.0    | 8.5 | v    | Notes 3, 5 |

| f <sub>φ1A</sub> , f <sub>φ1B</sub><br>f <sub>φ2A</sub> , f <sub>φ2B</sub>                                                | Maximum Transport Clock<br>Frequency                |     | 5.0    |     | MHz  | Note 5     |

| f <sub>øR</sub>                                                                                                           | Maximum Reset Clock<br>Frequency (Output Data Rate) |     | 10.0   |     | MHz  | Note 6     |

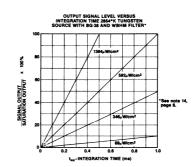

AC Characteristics: T<sub>c</sub> = 25°C,  $f_{oR}$  = 1.0 MHz,  $t_{int}$  = 320  $\mu$ s,  $t_{transport}$  = 259  $\mu$ s, Light Source = 2854°K + filters as specified. All operating voltages nominal specified values. (Note 1)

|        |                                                                              |                 | Range                |     |        | Condition             |

|--------|------------------------------------------------------------------------------|-----------------|----------------------|-----|--------|-----------------------|

| Symbol | Parameter                                                                    | Min             | Тур                  | Max | Unit   |                       |

| DR     | Dynamic Range<br>(relative to rms noise)<br>(relative to peak-to-peak noise) | 1250:1<br>250:1 | 2500:1<br>500:1      |     |        | Note 7                |

| NEE    | RMS Noise<br>Equivalent Exposure                                             |                 | 2 × 10 <sup>-4</sup> |     | μJ/cm² |                       |

| SE     | Saturation Exposure                                                          |                 | 0.5                  |     | μJ/cm² |                       |

| CTE    | Charge Transfer Efficiency                                                   |                 | 99.995               |     | %      | Note 8                |

| SR     | Spectral Response<br>Range Limits                                            |                 | 0.45 — 1.05          |     | μm     |                       |

| P      | Power Dissipation                                                            |                 | 100                  |     | mW     | V <sub>OD</sub> = 15V |

| z      | Output Impedance                                                             |                 | 1000                 |     | Ω      |                       |

| N      | RMS Noise<br>Peak-to-Peak Noise                                              |                 | 80<br>400            |     | μV     |                       |

Performance Characteristics:  $T_c = 25^{\circ}C$ ,  $f_{\phi R} = 1.0$  MHz,  $t_{int} = 320 \mu s$ ,  $t_{transport} = 259 \mu s$ , Light Source = 2854°K + filters as specified. All operating voltages nominal specified values. (Note 1)

|                  |                                                                         | Range |         |     |     |       |     |                       |            |

|------------------|-------------------------------------------------------------------------|-------|---------|-----|-----|-------|-----|-----------------------|------------|

|                  |                                                                         |       | CCD111A |     |     | CD111 | В   |                       |            |

| Symbol           | Characteristic                                                          | Min   | Тур     | Max | Min | Тур   | Max | Unit                  | Condition  |

| PRNU             | Photoresponse Non-uniformity Peak-to-Peak 2854°K + 700 nm cutoff filter |       | 35      | 70  |     | 25    | 70  | mV                    | 14, 15, 16 |

|                  | 2854°K + 900 nm cutoff filter                                           |       | 45      | 110 |     | 45    | 110 | mV                    | 14, 15, 16 |

|                  | 2854°K unfiltered                                                       |       | 70      |     |     | 60    |     | mV                    | 14, 15, 16 |

|                  | Single-pixel Positive Pulses                                            |       | < 10    |     |     | <10   |     | mV                    | 15, 16     |

|                  | Single-pixel Negative Pulses                                            | ١.    | 20      | 60  |     | 20    | 60  | mV                    | 15, 16     |

| RI               | Register Imbalance<br>('Odd'/'Even')                                    |       | <5      |     |     | <5    |     | mV                    | 15, 16     |

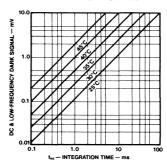

| DS               | Dark Signal DC Component                                                | 0     | <1      | 3   | 0   | 2     | 15  | mV                    | 2, 9, 10   |

|                  | Low Frequency Component                                                 | 0     | <1      | 2   | 0   | 2     | 10  | mV                    | 2, 9, 11   |

| SPDSNU           | Single-pixel DS Non-uniformity                                          | 0     | <1      | 2   | 0   | 1     | 2   | mV                    | 9, 11, 12  |

| PR               | Peripheral Response<br>2854°K + 700 nm cutoff filter                    |       | 10      | 17  |     | <2    | 5   | % of V <sub>OUT</sub> | 14         |

|                  | 2854°K + 900 nm cutoff filter                                           |       | 12      | 20  |     | 3     | 7   | % of V <sub>OUT</sub> | 14         |

|                  | 2854°K unfiltered                                                       |       | 25      |     |     | 4     |     | % of V <sub>OUT</sub> | 14         |

| R                | Responsivity<br>2854°K + 700 nm cutoff filter                           | 0.7   | 1.3     | 2.1 | 0.5 | 1.1   | 2.0 | V/µJ/cm²              | 13, 14     |

|                  | 2854°K + 900 nm cutoff filter                                           | 1.3   | 2.4     | 3.9 | 0.8 | 1.6   | 2.4 | V/µJ/cm²              | 13, 14     |

|                  | 2854°K unfiltered                                                       | 1     | 2.0     |     |     | 0.9   |     | V/µJ/cm²              | 13, 14     |

| V <sub>SAT</sub> | Saturation Output Voltage                                               | 500   | 900     |     | 500 | 900   |     | mV                    | 17         |

#### Notes

- T<sub>C</sub> is defined as the package temperature, measured on the back surface of the ceramic body.

Negative transients on any clock pin going below 0.0V may cause charge injection that results in an increase in the apparent Dark Signal. 2.

- 3.

- $\gamma_{\phi PH}$  should track  $\gamma_{RD}$ . The data output frequency  $\gamma_{\phi R}$  is twice that of each transport clock ( $\gamma_{\phi 1A}$ ,  $\gamma_{\phi 1B}$ ,  $\gamma_{\phi 2A}$ ,  $\gamma_{\phi 2B}$ ). The data output frequency  $\gamma_{\phi R}$  is twice that of each transport clock ( $\gamma_{\phi 1A}$ ,  $\gamma_{\phi 1B}$ ,  $\gamma_{\phi 2A}$ ,  $\gamma_{\phi 2B}$ ). The data output frequency is limited by the increase in Dark Signal.

- 5.

- Dynamic Range is defined as "V<sub>SAT</sub>/rms (temporal) Noise" or "V<sub>SAT</sub>/Peak-to-Peak (temporal) Noise." CTE is measured for a one-stage transfer.

- See photographs for Dark Signal definitions.

- DC and low-frequency Dark Signal components approximately double for every 5°C increase in T<sub>C</sub>. The shift register component is also 10.

- inversely proportional to f<sub>o.R</sub>.

Single-pixel Dark Signal non-uniformity (SPDSNU) approximately doubles for every 8°C increase in T<sub>C</sub>. They are also directly proportional to the integration time tint

- Each SPDSNU is measured from the DS level adjacent to the base of the SPDSNU. 12.

- RESPONSIVITY is defined as the "volts of video output" per "Incident Radiant Energy measured over the 350 nm-1200 nm band." The device will not respond to infrared wavelengths longer than = 1200 nm. However, 2/3 of the radiant energy from a 2854°K source is at λ>1200 nm. For the unfiltered 2854°K source, the responsivity values for light measured over 0 < \lambda < \infty will be ~0.3X of the responsivity values for light measured over 350 nm  $< \lambda <$  1200 nm.

#### Notes (cont'd)

- OPTICAL FILTERS: a "700 nm cutoff" filter is realized by using one "Wide Band Hot Mirror" (Optical Coating Labs, Inc., Santa Rosa, California) and one 2.0 mm thick "BG-38" blue glass (Schott Optical Glass, Duryea, Pennsylvania) filter in series. The "900 nm cutoff" filter is available on special order, consult Fairchild CCD Applications Engineering for details. Transmittance curves for the two cutoff filters and Spectral Energy Distribution curves for these filters with a 2854" K light source are given in the "Typical Performance Curves" section of this data sheet. It should be noted that the "2854" K | 700 nm cutoff" source is a good approximation to a Daylight Fluorescent bulb.

All PRNU measurements taken at a 350mV output level using a F/5.0 lens; all PRNU measurements exclude the outputs from the first and last

- 15. photoelements of the array. The "I" number is defined as the distance from the lens to the array divided by the diameter of the lens apprture. As f number increases, the resulting more highly collimated light causes package window aberrations to dominate and increase the PRNU. A lower f number (f <5) results in less collimated light, causing photosite blemishes to dominate PRNU. See photographs for PRNU definitions.

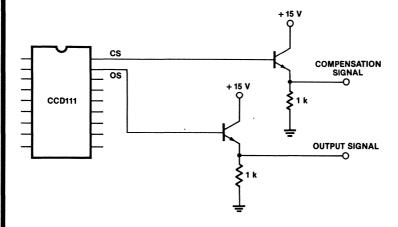

- See test load configuration.

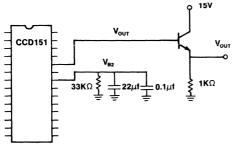

#### **Test Load Configuration**

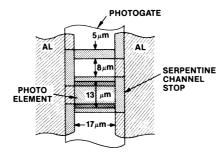

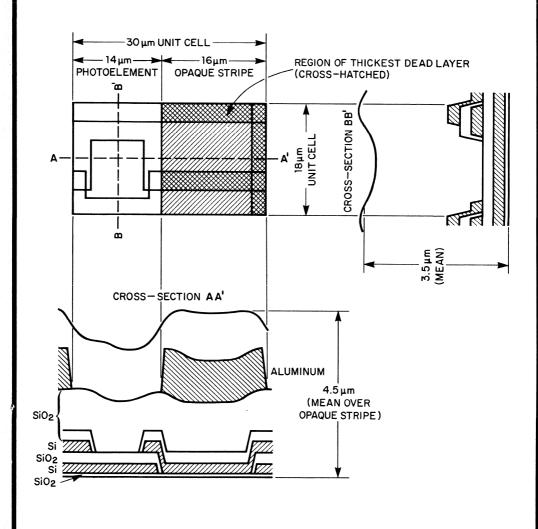

#### **Photoelement Dimensions**

#### ALL DIMENSIONS ARE TYPICAL VALUES.

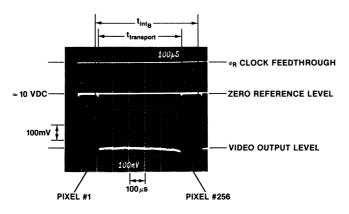

# **Output with Uniform Illumination**

**TEST CONDITIONS:**  $T_C = +25^{\circ}C$ ,  $t_{int} = 640 \mu s$ ,  $f_{gR} = 512 \text{ kHz}$ , "typ" voltage inputs,  $2854^{\circ}K + 700 \text{ nm}$  cutoff filter set. (Half standard test speeds for clearer photos.)

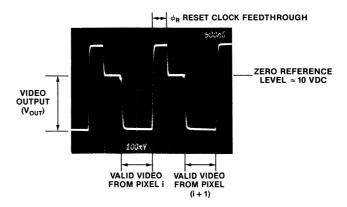

#### **Output of Two Pixels**

#### **DEVICE ILLUMINATED**

# **DEVICE IN DARK**

**TEST CONDITIONS:**  $T_C = +25^{\circ}C$ ,  $t_{int} = 640 \mu s$ ,  $f_{sR} = 512 \text{ kHz}$ , "typ" voltage inputs,  $2854^{\circ}K + 700 \text{ nm}$  cutoff filter set. (Half standard test speeds for clearer photos.)

# Photoresponse Non-uniformity

MEASURED AT V<sub>OUT</sub> = 350 mV; ALL PRNU COMPONENTS EXCLUDE PIXELS #1 AND #256.

TEST CONDITIONS: T\_C + 25 °C,  $t_{\rm int}$  = 320  $\mu$ s,  $t_{\rm eR}$  = 1.0 MHz, "typ" voltage inputs, 2854 °K + 700 nm cutoff filter set.

DC + Low Frequency Dark Signal

# AT $t_{int} = 900 \mu s$ , OTHER INPUTS SAME AS ABOVE:

**TEST CONDITIONS:**  $T_C = +25^{\circ}C$ ,  $t_{int} = (see above)$ ,  $t_{\phi R} = 512$  kHz, "typ" voltage inputs. (Half standard test speeds for clearer photos.)

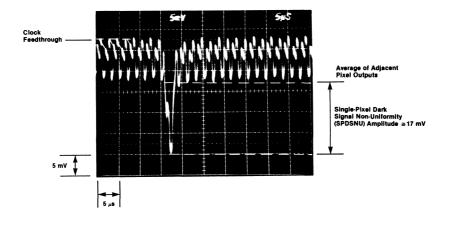

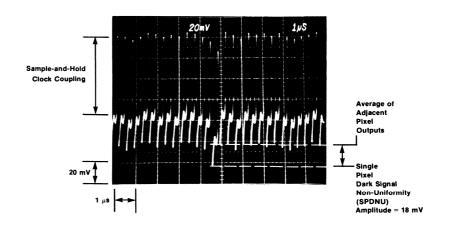

#### Single-pixel Dark Signal Non-uniformity

**TEST CONDITIONS:**  $T_C = +25^{\circ}C$ ,  $t_{int} = 2.560$  ms,  $f_{\phi R} = 128$  kHz, "typ" voltage inputs. (One-eighth standard test speeds to emphasize Dark Signal.)

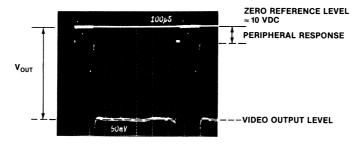

#### Peripheral Response

**TEST CONDITIONS:**  $T_C = +25^{\circ}C$ ,  $t_{int} = 640 \, \text{us}$ ,  $t_{gR} = 510 \, \text{kHz}$ , "typ" voltage inputs,  $2854^{\circ}K + 700 \, \text{nm}$  cutoff filter set. (Half standard test speeds for clearer photos.)

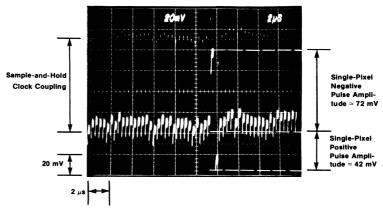

$_{\phi X}$ (Transfer Clock) Coupling into OS (Output)

**TEST CONDITIONS:**  $T_C = +25^{\circ}C$ ,  $T_{int} = 640 \mu s$ ,  $f_{sR} = 512 \text{ kHz}$ , "typ" voltage inputs,  $2854^{\circ}K + 700 \text{ nm}$  cutoff filter set. (Half standard test speeds for clearer photos.)

#### **Device Care and Operation**

Charge Injection: Every input pin has a gate protection structure that includes a diode from the input to the (grounded) substrate  $V_{SS}$ . The diode is reverse-biased during normal operation  $(v_{in} > V_{SS})$ . Negative (transient) input voltages  $(V_{in} < V_{SS})$  will forward-bias the dlode, injecting electrons into the bulk silicon of the CCD chip.

If sufficient charge is injected, it will accumulate in the transport register(s) and/or the photosites near the injecting gate protection structure(s). Injected charge which accumulates in the photosites will typically result in an apparent bell-shaped increase in Dark Signal (≈ 20-200 pixels wide) near the injecting gate protection structure. Injected charge which accumulates in a transport register will result in an apparent uniform increase in that register's low frequency dark signal, creating a noticeable increase in the apparent Register Imbalance ("odd/even") of the Dark Signal.

The susceptibility to charge injection sufficient to increase the DC and Low Frequency Dark Signal varies significantly from device to device. It is not possible to select devices with "low" susceptibility. However, devices with low Dark Signal are typically more susceptible than devices with high Dark Signal.

Sufficient charge to appear as increased DC and Low Frequency Dark Signal may be injected by negative transient voltages <4 ns long. Since these transients

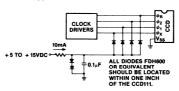

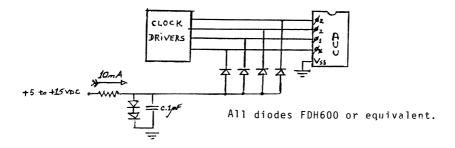

cannot be detected by oscilloscopes with less than 250-500 MHz bandwidth, a system which appears to be free from negative transients on a 200 MHz scope may still be prone to charge injection. The recommended method to eliminate charge injection is the following diode clipper circuit:

It is also important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The DC and Low Frequency Dark Signal approximately doubles for every 5°C temperature increase and Dark Signal Non-Uniformities approximately double for every 8°C increase. The devices may be cooled to achieve very long integration times and very low light level capability.

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with deionized water. Allow the glass to dry, preferably by blowing with filtered dry  $N_2$  or air.

#### **Typical Performance Curves**

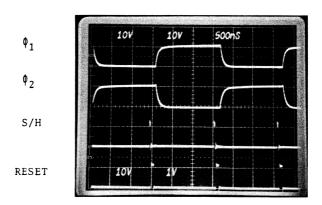

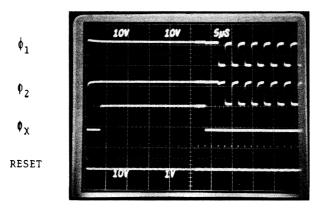

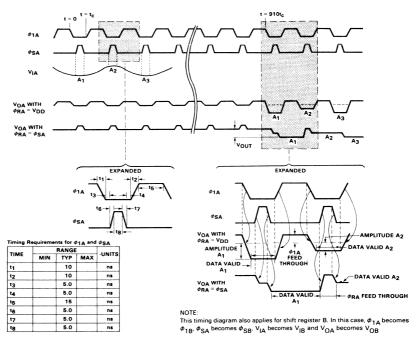

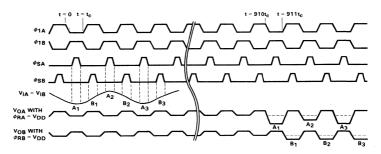

VIDEO DATA VALID FROM REGISTER A

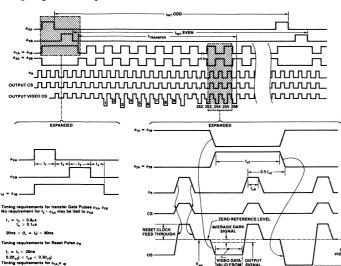

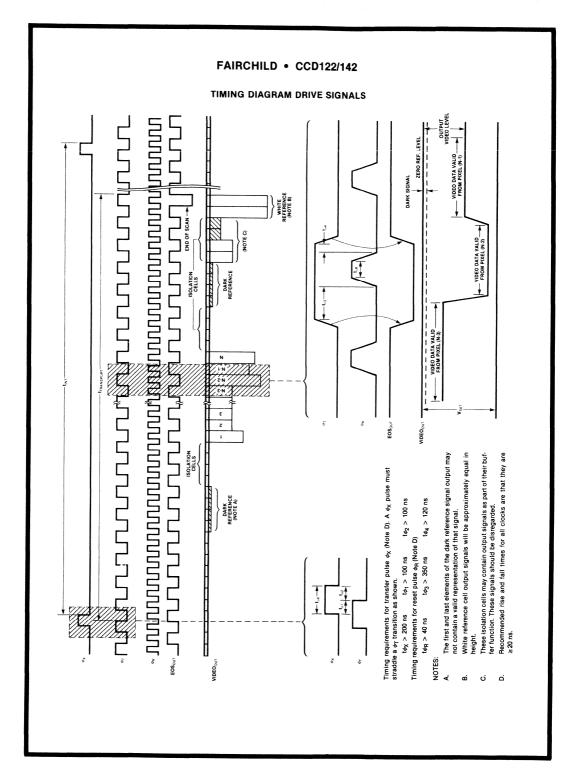

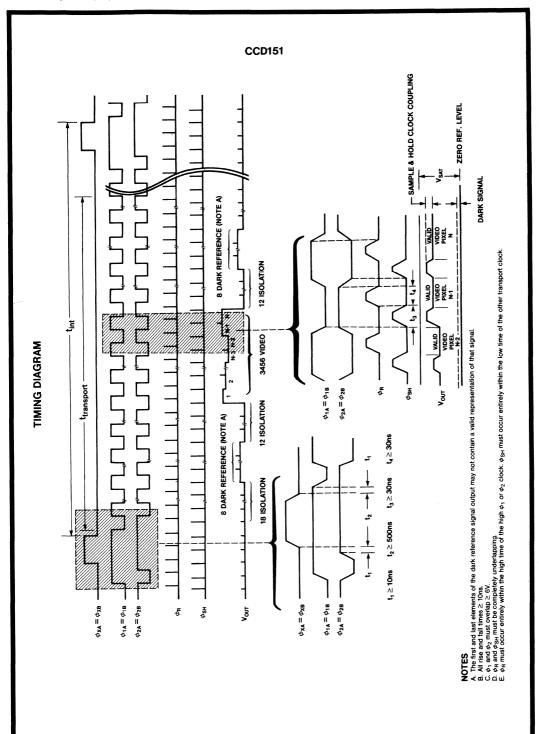

# **Timing Diagram Drive Signals**

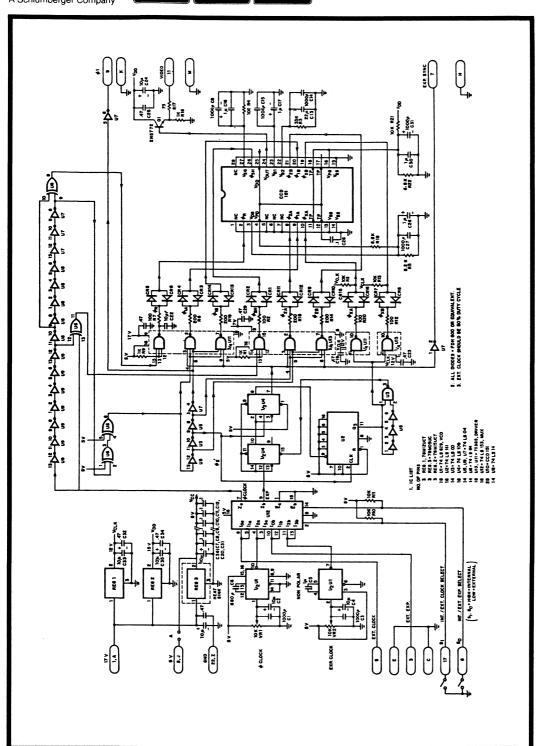

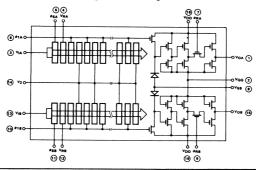

#### Circuit Diagram

20ns < (t, = t<sub>i</sub>) < 100ns

#### Order Information

It is important to note that two different selections of the CCD111 are being offered for applications that differ in the wavelength of light used for imaging. Please refer to the section "Major Differences Between the CCD111A and CCD111B" on page 3 before placing an order.

To order the CCD111, please follow the ordering codes listed in the table below:

| Description                       | Device Type<br>Order Code |

|-----------------------------------|---------------------------|

| CCD111A 256 x 1 Line Image Sensor | CD111ADC                  |

| CCD111B 256 x 1 Line Image Sensor | CD111BDC                  |

A printed circuit board is available which includes all the necessary clocks, logic drivers, and video amplifiers to operate the CCD111. The board is fully assembled and tested and requires ±15V and +5V supplies for operation. The printed circuit board order code is: CCD111DB.

For further information on the boards, please call your nearest Fairchild Sales Office. For technical assistance, call (415) 493-8001.

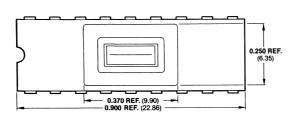

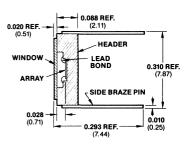

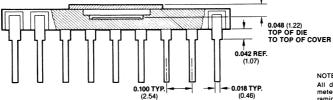

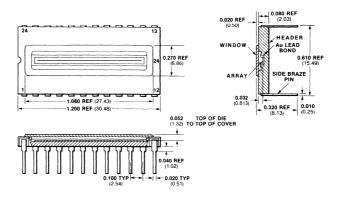

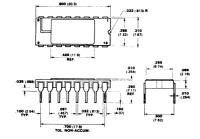

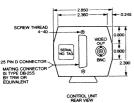

#### **CCD111DC Package Outline**

18-Pin Dual In-Line Ceramic Package

All dimensions in inches (bold) and milli-All dimensions in incnes (bodi) and millimeters (parentheses). Header is black ceramic (Al<sub>2</sub>O<sub>3</sub>). Glass window is attached to header with popxy coment. Photosicit #1 is located towards the notched end of the package. Terminal #9 is electronically connected to the Substrate (V<sub>SS</sub>).

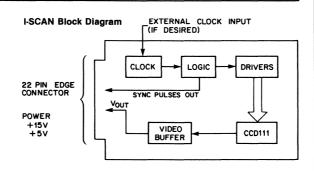

# ISCAN

# **DESIGN DEVELOPMENT SET**

The I-SCAN design development set is being specially offered by Fairchild as a low cost tool with which to gain understanding of charge-coupled devices principles. The set includes a Fairchild CCD111, 256 element line scan sensor, mounted on a printed circuit card that contains all the necessary CCD111 operating electronics.

I-SCAN is intended for use as a construction aid for experimental systems using CCD line scan sensors or can be incorporated directly into systems requiring 256 elements of resolution.

I-SCAN comes fully assembled and tested and requires only the input of power supplies and an oscilloscope to display the video information corresponding to the image placed in front of the sensor.

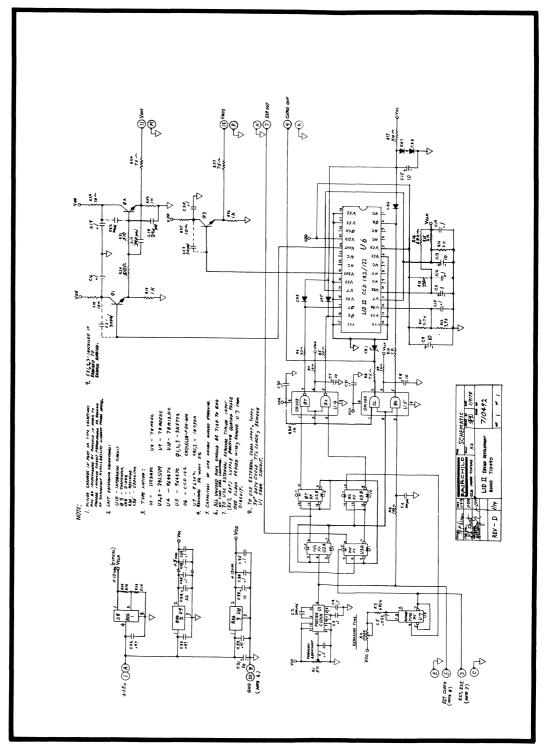

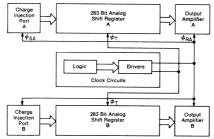

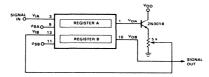

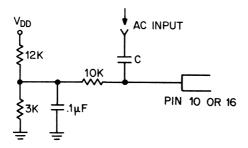

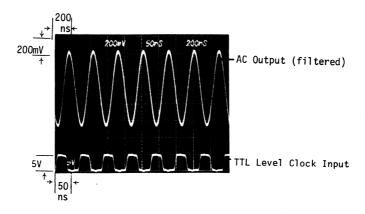

The I-SCAN printed circuit card (block diagram) includes a variable frequency clock generator that can be overriden by an external input, logic circuitry for timing the drive signals, drivers to interface the TTL logic to CCD levels and video buffer circuits.

Detailed schematics, a parts layout drawing and timing diagram are included with I-SCAN.

To operate the board, supply +5V and +15V through a 22-pin standard edge connector to the PC board. Video information as well as synchronization pulses are supplied to the connector for display on an oscilloscope.

To order I-SCAN, follow the order code below:

| Description                                         | Order Code |

|-----------------------------------------------------|------------|

| I-SCAN 256-Element Line Scan Design Development Set | I-SCAN     |

CCD Imaging "Sensing the Future"

# CCD112 256-Element Line Scan Image Sensor

# **Preliminary**

**CCD** Imaging

#### DESCRIPTION

The CCD112 is a monolithic 256-element line image sensor. The device is designed for optical character recognition and other imaging applications that require high sensitivity and high speed.

The CCD112 has overall improved performance compared with the CCD111 including higher sensitivity, an enhanced blue response and a lower dark signal. The devices also incorporate on-chip clock driver circuitry.

The photoelement size is  $13\mu$ m (0.51 mils) by  $13\mu$ m (0.51 mils) on  $13\mu$ m (0.51 mils) centers. The device is manufactured using Fairchild advanced charge-coupled device n-channel Isoplanar buried-channel technology.

#### **FEATURES**

- ENHANCED SPECTRAL RESPONSE (PARTICULARLY IN THE BLUE REGION)

- LOW DARK SIGNAL

- · HIGH RESPONSIVITY

- ON-CHIP CLOCK DRIVERS

- DYNAMIC RANGE TYPICAL: 2500:1

- OVER 1V PEAK-TO-PEAK OUTPUTS

- DARK REFERENCE CONTAINED IN A SAMPLED-AND-HELD OUTPUT

- · SINGLE POWER SUPPLY

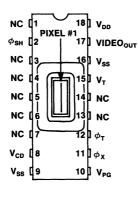

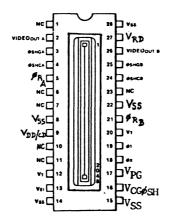

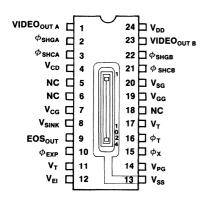

#### CONNECTION DIAGRAM DIP (TOP VIEW)

#### PIN NAMES

Photogate  $V_{PG}$  $\phi_{\mathsf{X}}$ Transfer Clock Transport Clock VIDEOOUT **Output Amplifier Source**  $V_{DD}$ **Output Amplifier Drain**  $V_{CD}$ Clock Driver Drain **Analog Transport Shift Registers** DC Electrode  $\phi_{\mathsf{SH}}$ Sample-and-Hold Gate V<sub>ss</sub> NC Substrate (GND) No Connection (Do not Ground)

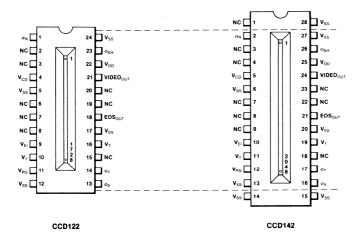

# CCD122/142

The CCD142 is no longer carried. It has been replaced by the CCD143.

# 1728/2048-ELEMENT LINEAR IMAGE SENSOR

FAIRCHILD CHARGE COUPLED DEVICE

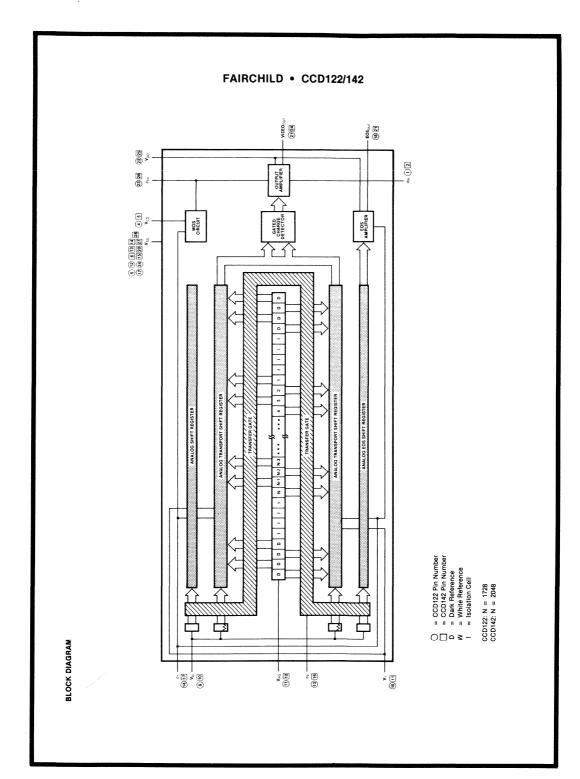

GENERAL DESCRIPTION-The CCD122 and CCD142 are monolithic 1728 and 2048-element line image sensors, respectively. The devices are designed for page scanning applications including facsimile, optical character recognition and other imaging applications which require high resolution and high sensitivity.

The 1728 sensing elements of the CCD122 provide a 200-line per inch resolution across an 8-1/2 inch page adopted as an international facsimile standard. The 2048 sensing elements of the CCD142 provide an 8-line per millimeter resolution across a 256 millimeter page adopted as the Japanese facsimile standard.

The CCD122 and the CCD142 have overall improved performance compared with the CCD121H including higher sensitivity, an enhanced blue response and a lower dark signal. The devices also incorporate on-chip clock driver circuitry.

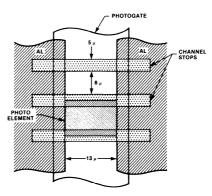

The photoelement size is 13  $\mu$  (0.51 mils) by 13  $\mu$  (0.51 mils) on 13  $\mu$  (0.51 mils) centers. The devices are manufactured using Fairchild advanced charge-coupled device n-channel Isoplanar buried-channel technology.

- ENHANCED SPECTRAL RESPONSE (PARTICULARLY

- IN THE BLUE REGION)

- LOW DARK SIGNAL HIGH RESPONSIVITY

- ON-CHIP CLOCK DRIVERS

- DYNAMIC RANGE TYPICAL: 2500:1

- OVER 1V PEAK-TO-PEAK OUTPUT

- . DARK AND WHITE REFERENCES CONTAINED IN A

- SAMPLED-AND-HELD OUTPUT

- . SINGLE POWER SUPPLY

#### PIN NAMES

$V_{PG}$

| φχ              | Transfer Clock                  |

|-----------------|---------------------------------|

| φτ              | Transport Clock                 |

| VIDEOOUT        | Output Amplifier Source         |

| V <sub>DD</sub> | Output Amplifier Drain          |

| φR              | Reset Clock                     |

| VcD             | Clock Driver Drain              |

| VEI             | Electrical Input Bias           |

| Vτ              | Analog Transport Shift Register |

|                 | DC Electrode                    |

| <b>EOS</b> out  | End-of-Scan Output              |

| фѕн             | Sample-and-Hold Clock           |

| Vss             | Substrate (GND)                 |

| NC              | No Connection (Do not Ground)   |

**Photogate**

# CCD122/142 VS. CCD121H COMPARISON

| PARAMETER                                                                                                                      | CCD122/142                                                                  | CCD121H                        |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------|

| Spectral Response — Blue Overall  Dark Signal Responsivity On-Chip Clock Drivers Dark and White References Single Power Supply | 4:1 Improvement 2:1 Improvement 2:1 Improvement 2:1 Improvement Yes Yes Yes | <br><br><br><br>No<br>No<br>No |

#### CONNECTION DIAGRAM DIP (TOP VIEW)

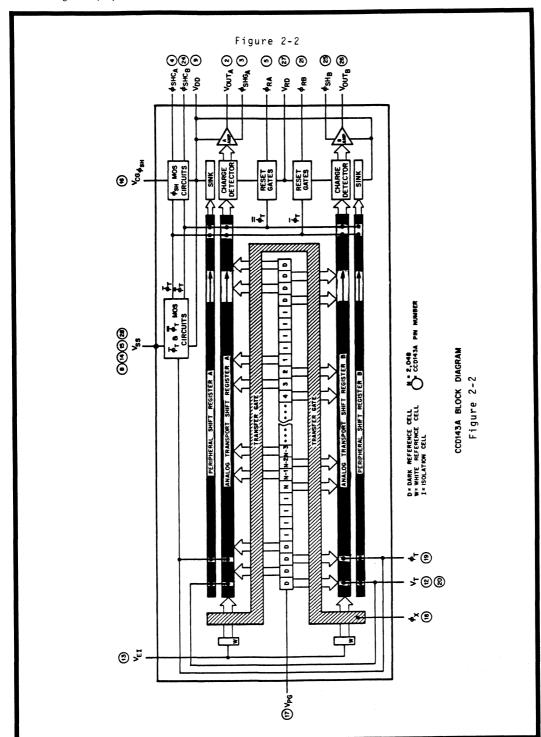

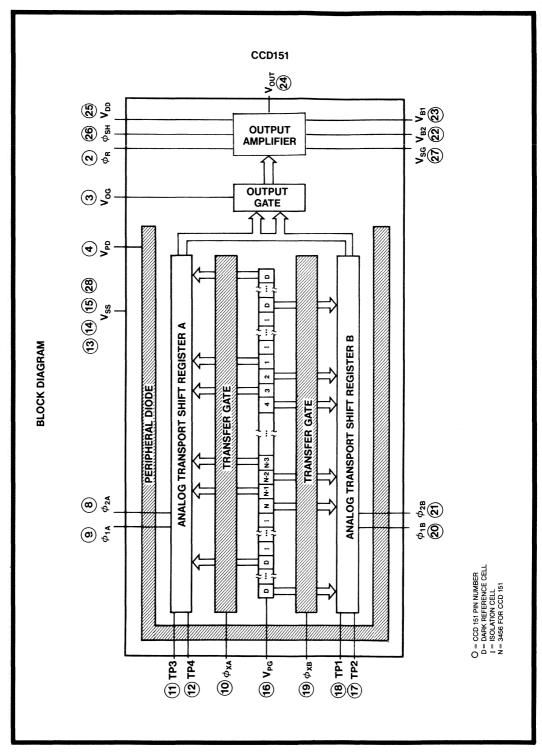

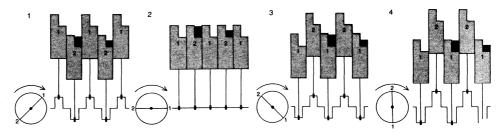

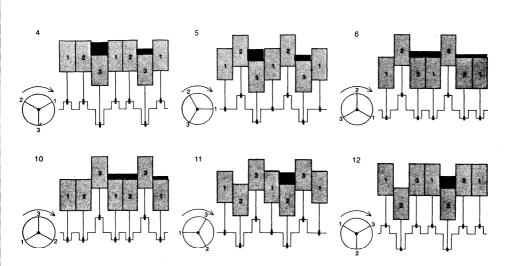

**FUNCTIONAL DESCRIPTION**—The CCD122/142 consists of the following functional elements illustrated in the Block Diagram:

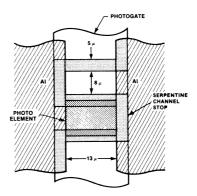

Image Sensor Elements — A line of 1728/2048 image sensor elements separated by diffused channel stops and covered by a silicon dioxide surface passivation layer. Image photons pass through the transparent silicon dioxide layer and are absorbed in the single crystal silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated noise background at zero illumination to a maximum at saturation under bright illumination.

Transfer Gate — Gate structure adjacent to the line of image sensor elements. The charge-packets accumulated in the image sensor elements are transferred out via the transfer gate to the transport registers whenever the transfer gate voltage goes HIGH. Alternate charge-packets are transferred to the analog transport shift registers. The transfer gate also controls the exposure time for the sensing elements and permits entry of charge to the End-Of-Scan (EOS) shift registers creating the end-of-scan waveform.

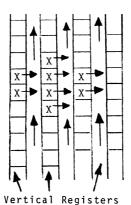

Four 879/1039-Bit Analog Shift Registers — Two on each side of the line of image sensor elements and separated from it by the transfer gate. The two inside resisters, called the transport shift registers, are used to move the image generated charge-packets delivered by the transfer gate serially to the charge-detector/amplifier. The complementary phase relationship of the last elements of the two transport shift registers provides for alternate delivery of

charge-packets to establish the original serial sequence of the line of video in the output circuit. The outer two registers serve to deliver the end-of-scan waveform and reduce peripheral electron noise in the inner shift registers.

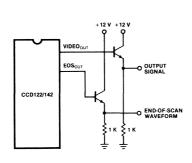

**Gated Charge-Detector/Amplifer** — Charge-packets are transported to a precharged diode whose potential changes linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of an n-channel MOS transistor producing a signal which passes through the sample-and-hold gate to the output at VIDEOour. The sample-and-hold gate is a switching MOS transistor in the output amplifier that allows the output to be delivered as a sampled-and-held waveform. A reset transistor is driven by the Reset Clock  $\langle \phi a \rangle$  and recharges the charge-detector diode capacitance before the arrival of each new signal charge-packet from the transport registers.

Clock Driver Circuitry — Allows the CCD122/142 to be operated using only three external clocks, (1) a Reset Clock signal which controls the integrated output signal amplifier, (2) a square wave Transport Clock which operates at half the reset clock frequency and controls the readout rate of video data from the sensor, and (3) a Transfer Clock pulse which controls exposure time of the sensor. The external clocks should be able to supply TTL level power.

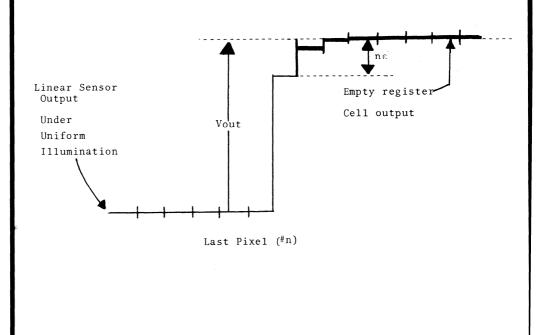

Dark and White Reference Circuitry — Four additional sensing elements at both ends of the 1728/2048 array are covered by opaque metalization. They provide a dark (no illumination) signal reference which is delivered at both ends of the line of video ouptut representing the illuminated 1728/2048 sensor elements (labelled "D" in the block diagram). Also included at one end of the 1728/2048 sense element array is a white signal reference level generator which likewise provides a reference in the output signal (labelled "W" in the block diagram). These reference levels are useful as inputs to external DC restoration and/or automatic gain control circuitry.

#### **DEFINITION OF TERMS:**

Charge-Coupled Device — A charge-coupled device is a semiconductor device in which finite isolated charge-packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge-packets are minority carriers with respect to the semiconductor substrate.

**Transfer Clock**  $\phi x$  — The voltage waveform applied to the transfer gate to move the accumulated charge from the image sensor elements to the CCD transport shift registers.

**Transport Clock**  $\phi$ T — The clock applied to the gates of the CCD transport shift registers to move the charge-packets received from the image sensor elements to the gated charge-detector/amplifier.

Gated Charge-Detector/Amplifier — The output circuit of the CCD122/142 which receives the charge-packets from the CCD transport shift registers and provides a signal voltage proportional to the size of each charge-packet received. Before each new charge-packet is sensed, a reset clock returns the charge-detector voltage to a fixed base level.

**Reset Clock**  $\phi R$  — The voltage waveform required to reset the voltage on the charge-detector.

Sample-and-Hold Clock  $\phi$ SH — An internally supplied voltage waveform applied to the sample-and-hold gate in the amplifier to create a continuous sampled video signal at the output. The sample-and-hold feature can be defeated by connecting  $\phi$ SH to VDD.

**Dark Reference** — Video output level generated from sensing elements covered with opaque metalization providing a reference voltage equivalent to device operation in the dark. Permits use of external dc restoration circuitry.

White Reference — Video output level generated by on-chip circuitry providing a reference voltage permitting external automatic gain control circuitry to be used. The reference voltage is produced by charge-injection under the control of the electrical input bias voltage (VE). The amplitude of the reference is typically 70% of the saturation output voltage.

Isolation Cell — A site on-chip producing an element in the video output that serves as a buffer between valid video data and dark and white reference signals. The output from an isolation cell contains no valid video information and should be ignored.

**Dynamic Range** — The saturation exposure divided by the peak-to-peak noise equivalent exposure. (This does not take into account any dark signal components.) Dynamic range is

sometimes defined in terms of rms noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times rms noise.

**Peak-to-Peak Noise Equivalent Exposure** — The exposure level which gives an output signal equal to the peak-to-peak noise level at the output in the dark.

Saturation Exposure — The minimum exposure level that will produce a saturated output signal. Exposure is equal to the light intensity times the photosite integration time.

Charge Transfer Efficiency — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

**Spectral Response Range** — The spectral band in which the response per unit of radiant power is more than 10% of the peak response.

Responsivity — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure level.

**Dark Signal** — The output signal in the dark caused by thermally generated electrons which is a linear function of integration time and highly sensitive to temperature. (See accompanying photos for details of defintion.)

**Total Photoresponse Non-Uniformity** — The difference of the response levels between the most and least sensitive elements under uniform illumination. (See accompanying photos for details of definition.)

Saturation Output Voltage — The maximum usable signal output voltage, measured from the zero reference level. (See timing diagram.) Any photoelement whose video output < saturation output voltage has an in-spec charge transfer efficiency (CTE). CTE will be below the specification if the video output ≥ saturation output voltage.

Integration Time — The time interval between the falling edges of any two successive transfer pulses  $\phi x$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

Pixel - Picture element (photosite).

#### **TEST LOAD CONFIGURATION**

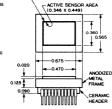

#### PHOTOELEMENT DIMENSIONS

All dimensions are typical values

# ABSOLUTE MAXIMUM RATINGS (Above which useful life may be impaired)

| Storage T | emperature                                                                                                               | - 25°C to + 125°C            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Operating | Temperature (See curves)                                                                                                 | - 25 °C to + 70 °C           |

| CCD122:   | Pins 1, 4, 9, 10, 11, 13, 14, 16, 22, 23<br>Pins 5, 12, 17, 24<br>Pins 2, 3, 6, 7, 8, 15, 18, 19, 20, 21                 | – 0.3 V to 15 V<br>0 V<br>NC |

| CCD142:   | Pins 2, 5, 10, 11, 12, 16, 17, 19, 25, 26<br>Pins 6, 13, 14, 15, 20, 27, 28<br>Pins 1, 3, 4, 7, 8, 9, 18, 21, 22, 23, 24 | - 0.3 V to 15 V<br>0 V<br>NC |

CAUTION NOTE: These devices have limited built-in gate protection. It is recommended that static discharge be controlled and minimized. Care must be taken to avoid shorting pins VIDEOOUT and EOSOUT to VSS or VDD during operation of the devices. Shorting these pins temporarily to VSS or VDD may destroy the output amplifiers.

#### DC CHARACTERISTICS: TP = 25°C (Note 1)

| SYMBOL | CHARACTERISTIC                        |      | RANGE | UNITS | CONDITIONS |            |

|--------|---------------------------------------|------|-------|-------|------------|------------|

|        | ONALIA OTENIO TIO                     | MIN  | TYP   | MAX   | UNITS      | CONDITIONS |

| Vcd    | Clock Driver Drain Supply Voltage     | 12.0 | 13.0  | 14.0  | V          |            |

| ICD    | Clock Driver Drain Supply Current     |      | 6.9   | 12.5  | mA         |            |

| VDD    | Output Amplifier Drain Supply Voltage | 12.0 | 13.0  | 14.0  | V          |            |

| IDD    | Output Amplifier Drain Supply Current |      | 6.9   | 12.5  | mA         |            |

| VPG    | Photogate Bias Voltage                | 6.5  | 7.0   | 7.5   | V          |            |

| VT     | DC Electrode Bias Boltage             | 4.5  | 5.0   | 5.5   | V          | Note 2     |

| VEI    | Electrical Input Bias Voltage         |      | 11.4  |       | V          | Note 3     |

| Vss    | Substrate (Ground)                    |      | 0.0   |       | V          |            |

# AC CHARACTERISTICS: (Note 1)

$TP = 25^{\circ}C$ ,  $f \phi R = 0.5$  MHz,  $t_{int} = 10$  ms, light source = 2854°K + 3.0 mm thick Corning 1-75 IR-absorbing filter. All operating voltages nominal specified values.

| SYMBOL     | CHARACTERISTIC                   |        | RANGE    | UNITS | CONDITIONS         |                                         |

|------------|----------------------------------|--------|----------|-------|--------------------|-----------------------------------------|

|            |                                  | MIN    | TYP      | MAX   | 7 014113           | CONDITIONS                              |

| DR         | Dynamic Range                    |        |          |       |                    |                                         |

|            | (relative to peak-to-peak noise) | 250:1  | 500:1    |       | 1                  | Note 9                                  |

|            | (relative to rms noise)          | 1250:1 | 2500:1   |       |                    |                                         |

| NEE        | RMS Noise Equivalent Exposure    |        | 0.0002   |       | μj/cm <sup>2</sup> | Note 10                                 |

| SE         | Saturation Exposure              |        | 0.4      |       | μj/cm <sup>2</sup> | Note 11                                 |

| CTE        | Charge Transfer Efficiency       |        | 0.999995 |       |                    | Note 12                                 |

| <b>V</b> o | Output DC Level                  | 3.0    | 5.5      | 10.0  | V                  | *************************************** |

| Z          | Output Impedance                 |        | 1.4      | 3.0   | kΩ                 |                                         |

| P          | On-Chip Power Dissipation        |        |          |       |                    |                                         |

|            | Clock Drivers                    |        | 90       | 150   | mW                 |                                         |

|            | Amplifiers                       | l .    | 90       | 150   | mW                 |                                         |

| N          | Peak-to-Peak Noise               |        | 2.0      |       | mV                 |                                         |

#### CLOCK CHARACTERISTICS: TP = 25°C (Note 1)

| SYMBOL | CHARACTERISTIC                                      |      | RANGE | UNITS | CONDITIONS |            |

|--------|-----------------------------------------------------|------|-------|-------|------------|------------|

|        |                                                     | MIN  | TYP   | MAX   | J          | CONDITIONS |

| Vφτι   | Transport Clock LOW                                 | 0.0  | 0.3   | 0.5   | V          | Notes 4, 5 |

| Vфтн   | Transport Clock HIGH                                | 9.75 | 10.0  | 10.5  | V          | Note 5     |

| VφxL   | Transfer Clock LOW                                  | 0.0  | 0.3   | 0.5   | ٧          | Notes 4, 6 |

| Vфхн   | Transfer Clock HIGH                                 | 9.75 | 10.0  | 10.5  | ٧          | Note 6     |

| VφRL   | Reset Clock LOW                                     | 0.0  | 0.3   | 0.5   | V          | Note 7     |

| VφRH   | Reset Clock HIGH                                    | 9.75 | 10.0  | 10.5  | V          | Note 7     |

| fφR    | Maximum Reset Clock Frequency<br>(Output Data Rate) | 1.0  | 2.0   |       | MHz        | Note 8     |

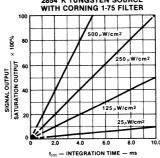

#### PERFORMANCE CHARACTERISTICS: (Note 1)

$T_P = 25\,^{\circ}\text{C}$ ,  $f\phi R = 0.5$  MHz, tint = 10 ms, light source = 2854  $^{\circ}\text{K}$  + 3.0 mm thick Corning 1-75 IR-absorbing filter. All operating voltages nominal specified values.

| SYMBOL | CHARACTERISTIC                                                 |                                | RANGE | UNITS | CONDITIONS                      |              |

|--------|----------------------------------------------------------------|--------------------------------|-------|-------|---------------------------------|--------------|

|        | CHARACTERISTIC                                                 | MIN                            | TYP   | MAX   | ] """                           | CONDITIONS   |

| PRNU*  | Photoresponse Non-uniformity                                   | to your teachers, and a second |       |       |                                 |              |

|        | Peak-to-Peak                                                   |                                | 160   | 210   | mV                              | Note 16      |

|        | Peak-to-Peak without Single-Pixel Positive and Negative Pulses | -                              | 100   |       | mV                              | Note 16      |

|        | Single-pixel Positive Pulses                                   |                                | 85    |       | mV                              | Note 16      |

|        | Single-pixel Negative Pulses                                   |                                | 130   |       | mv ]                            | Note 16      |

|        | Register Imbalance ("Odd"/"Even")                              |                                | 20    |       | mV                              | Note 16      |

| DS     | Dark Signal                                                    |                                |       |       |                                 |              |

|        | DC Component                                                   |                                | 5     | 15    | mV                              | Notes 13, 14 |

|        | Low Frequency Component                                        |                                | 5     | 10    | mV                              | Notes 13, 14 |

| SPDSNU | Single-pixel DS Non-uniformity                                 |                                | 20    | 40    | mV                              | Notes 13, 15 |

| R      | Responsivity                                                   | 2.0                            | 3.5   | 5.0   | Volts per<br>μj/cm <sup>2</sup> | Note 17      |

| VSAT   | Saturation Output Voltage                                      | 800                            | 1400  | 1600  | mV                              | Note 18      |

\*All PRNU Measurements taken at a 700 mV output level using an f/2.8 lens and excluded the outputs from the first and last elements of the array. The "f" number is defined as the distance from the lens to the array divided by the diameter of the lens aperture. As the f number increases, the resulting more highly columnated light causes the package window aberrations to dominate and increase PRNU. A lower f number results in less columnated light causing device photosite blemishes to dominate the PRNU.

#### NOTES:

- TP is defined as the package temperature.

- VT should be equal to (1/2) VoTH.

- VEI is used to generate the end-of-scan output and the white reference output. These two signals can be eliminated by connecting VEI to a voltage level equal to VφXH + 5 V.

- Negative transients on any clock pin going below 0.0 V may cause charge-injection which results in an increase of apparent DS.

- CoT ≈ 700 pF

- $C\phi X \cong 300 pF$   $C\phi R \cong 5 pF$ 6.

- Minimum clock frequency is limited by increase in dark signal.

- 10.

- Dynamic range is defined as VSAT/peak-to-peak (temporal) or VSAT/rms noise.

1 μ/cm² = 0.02 fcs at 2854\*K, 1 fcs = 50 μ/cm² at 2854\*K.

SE for 2854\*K for light without 3.0 mm thick Corning 1.75 IR-absorbing filter is typically 0.8 μ/cm².

- 11. 12. CTE is the measurement for a one-stage transfer.

- 13. See photographs for DS definitions.

- Dark signal component approximately doubles for every 5°C increase in TP. 14.

- Each SPDSNU is measured from the DS level adjacent to the base of the SPDSNU. The SPDSNU approximately doubles for every 8°C In-15. crease in TP.

- See photographs for PRNU definitions.

- Responsivity for 2854\*K light source without 3.0 mm thick Corning 1-75 IR-absorbing filter is typically 2 V per μ/cm<sup>2</sup>.

- 18 See test load configurations.

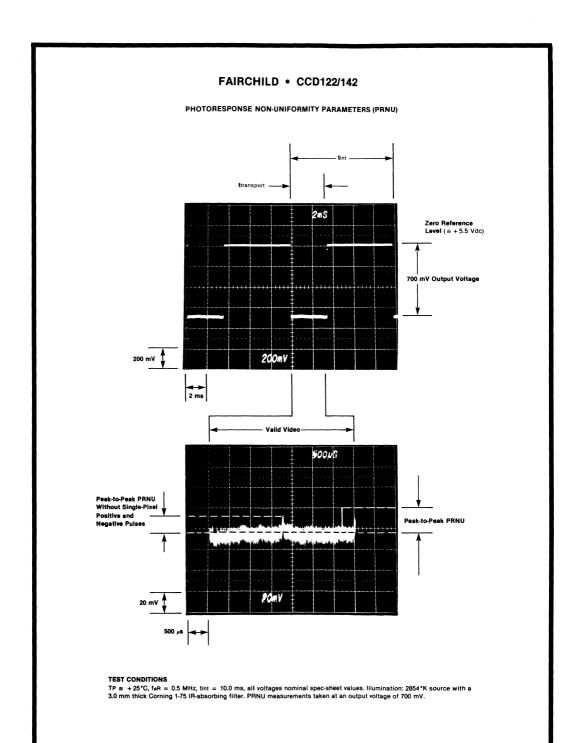

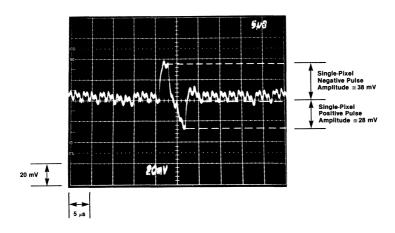

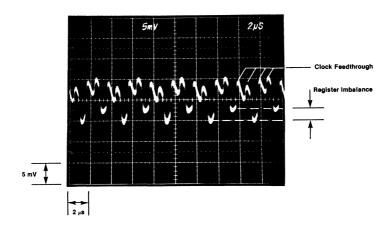

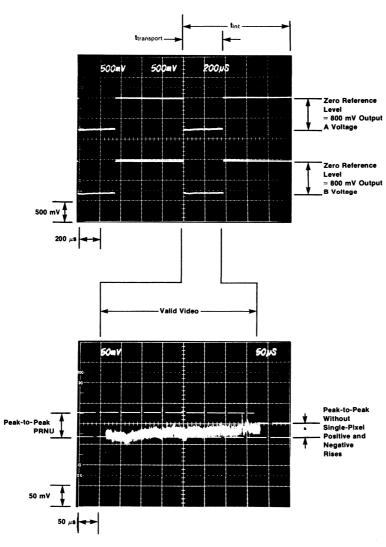

PRNU PARAMETERS (CONTINUED)

#### **TEST CONDITIONS**

TP ≈ +25°C, feR = 0.5 MHz, tint = 10.0 ms, all voltages nominal spec-sheet values. Illumination: 2854°K source with a 3.0 mm thick Corning 1-75 IR-absorbing filter. PRNU measurements taken at an output voltage of 700 mV.

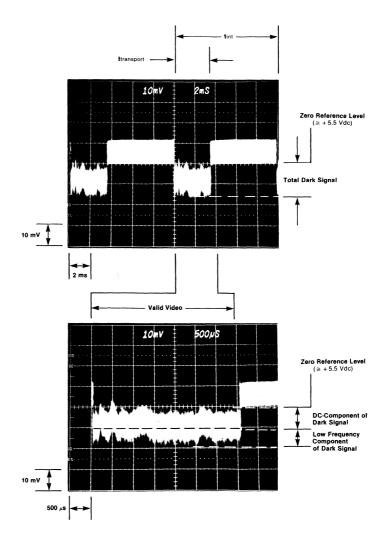

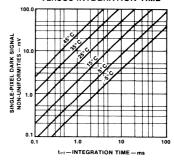

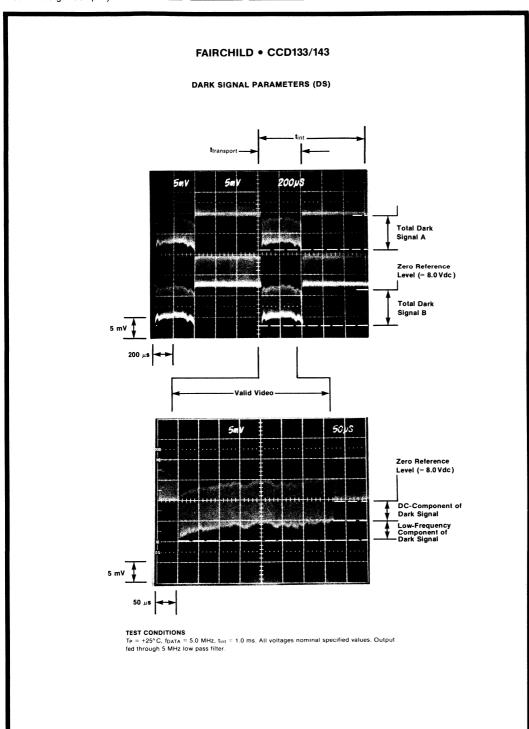

## DARK SIGNAL PARAMETERS (DS)

## TEST CONDITIONS

TP  $\cong$  +25°C, f $\phi$ R = 0.5 MHz, tint = 10.0 ms, all voltages nominal specified values.

DS PARAMETERS (CONTINUED)

#### **TEST CONDITIONS**

TP  $\cong$  +25°C, f $_{\phi}$ R = 0.5 MHz, tint = 10.0 ms, all voltages nominal specified values.

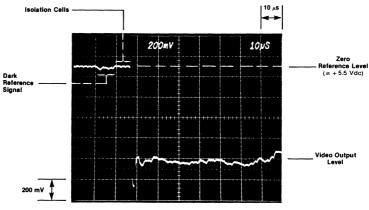

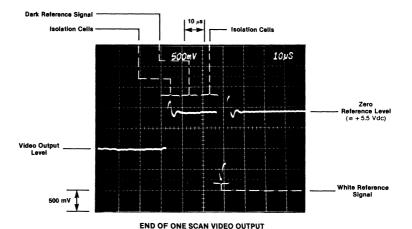

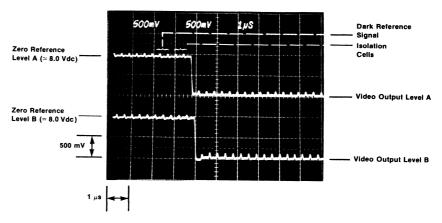

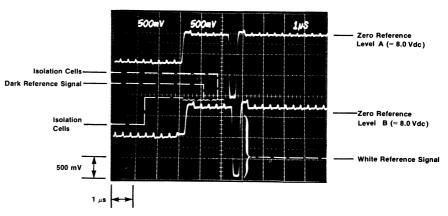

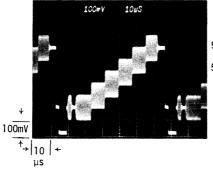

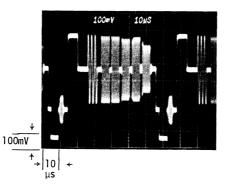

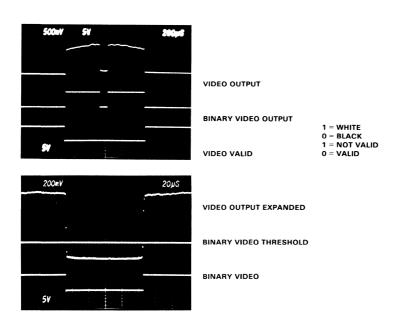

#### **VIDEO OUPUT TIMING PHOTOGRAPHS**

TEST CONDITIONS

TP = + 25°C, feR = 0.5 MHz, tint = 10 ms, all voltages nominal spec-sheet values. Illumination: 2854°K source with a 3.0 mm thick Corning 1-75 IR-absorbing filter. PRNU measurements taken at an output voltage of 700 mV.

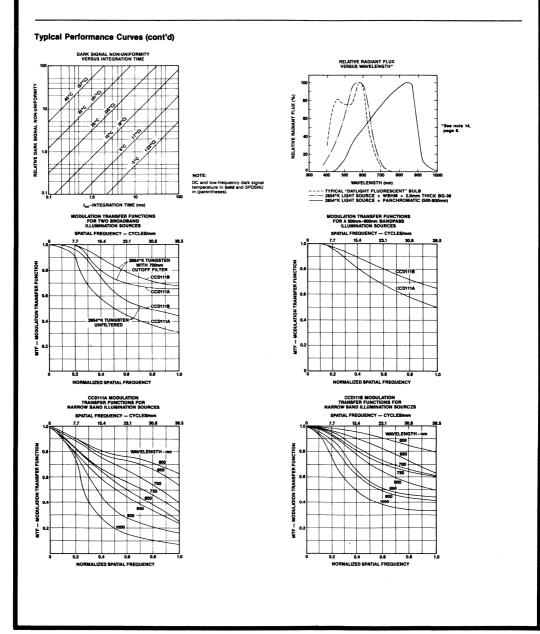

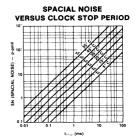

#### **TYPICAL PERFORMANCE CURVES**

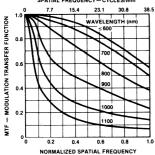

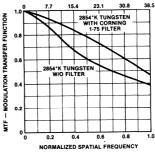

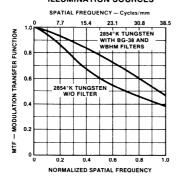

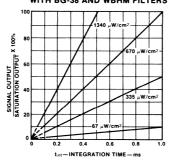

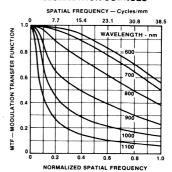

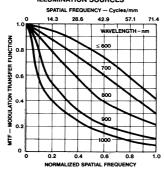

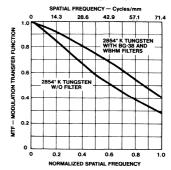

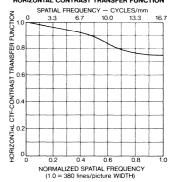

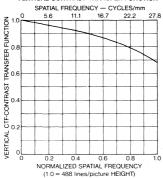

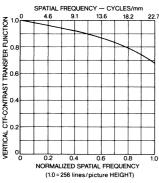

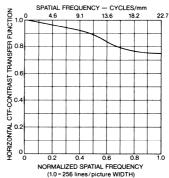

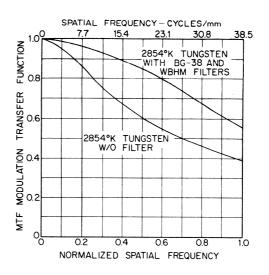

#### MODULATION TRANSFER FUNCTIONS FOR NARROW BAND ILLUMINATION SOURCES

SPATIAL FREQUENCY-CYCLES/mm

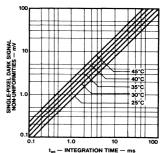

#### SINGLE-PIXEL DARK SIGNAL NON-UNIFORMITIES

#### MODULATION TRANSFER FUNCTIONS FOR TWO BROADBAND ILLUMINATION SOURCES

SPATIAL FREQUENCY — CYLES/mm

The Corning 1.75 filter has the following typical transmittance spectral characteristic: >85% at <600 nm, 60% at 700 nm, 30% at 800 nm, 5% at 900 nm and <2% at >1000 nm.

#### **DEVICE CARE AND OPERATION:**

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with de-ionized water. Allow the glass to dry preferably by blowing with filtered dry N2 or air.

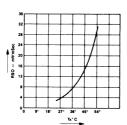

It is important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The dark signal DC and low frequency components approximately double for every 5°C temperature increase and single-pixel dark signal non-uniformities approximately double for every 8°C temperature increase. The devices may be cooled to achieve very long integration times and very low light level capability.

**ORDER INFORMATION** — Order CCD122DC where "D" stands for a ceramic package and "C" for commercial temperature range.

The pins on the CCD122DC and the CCD142DC are arranged to allow the 24-pin CCD122DC to be placed in a 28-pin CCD142DC socket. To do so, the CCD122DC is positioned in the center of the 28-pin socket such that Pin 1 of the device aligns with Pin 2 of the socket and Pin 12 of the device with Pin 13 of the socket.

Also available are printed circuit boards that include all the necessary clocks, logic drivers and video amplifiers to operate the CCD122DC or CCD142DC. The boards are fully assembled and tested and require only one power supply for operation (+ 15 V). The printed circuit board order codes are: CCD122DB, CCD142DB. For further information on the boards please call your nearest Fairchild sales office. For any technical assistance, call (415) 493-8001.

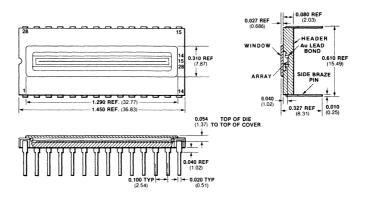

#### CCD122DC PACKAGE OUTLINE

24-Pin Dual In-line Ceramic Package

#### CCD142DC PACKAGE OUTLINE

28-Pin Dual In-line Ceramic Package

#### NOTES:

All dimensions in inches (bold) and millimeters (parenthesis). Header is black ceramic ( $Al_2O_3$ ). Window is glass. The amplifier of the device is located near the notched end of the package.

(THE CCD142 DEVELOPMENT BOARD IS NO LONGER AVAILABLE)

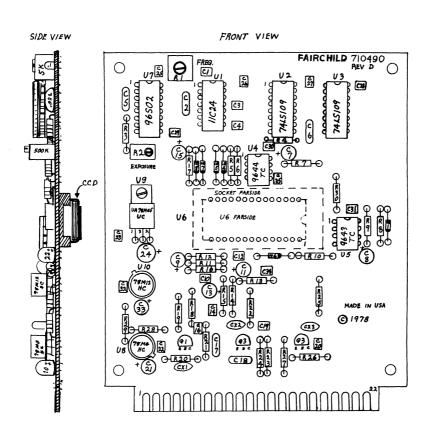

## CCD122 AND CCD142DB DESIGN DEVELOPMENT BOARDS

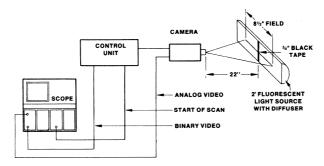

The Fairchild CCD122DB and CCD142DB design development boards are printed circuit cards which are intended for use as educational aids for gaining understanding of the operating characteristics of Fairchild CCD122 and CCD142 line scan image sensors and for use in assembly of experimental systems using the line scan sensors. The design development boards are sold fully assembled and tested, and require only connection of a single power supply input of +15V and connection of an oscilloscope to display the video information detected by the sensor.

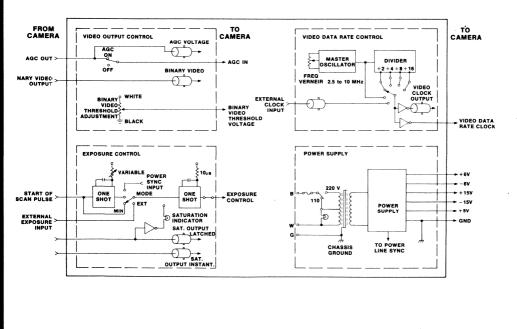

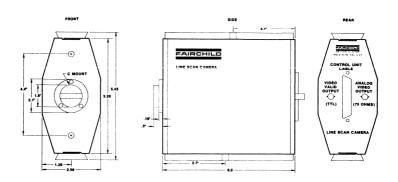

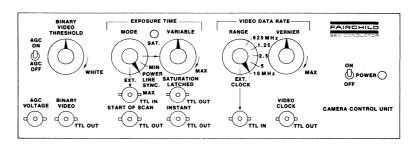

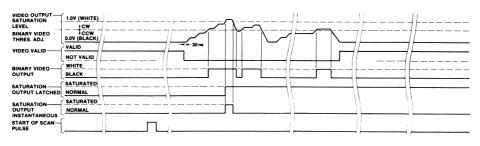

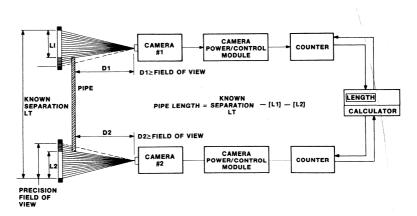

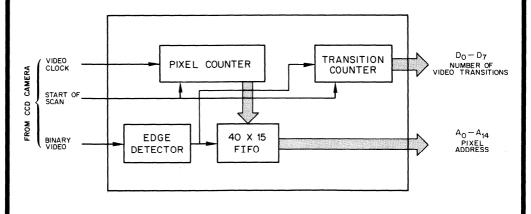

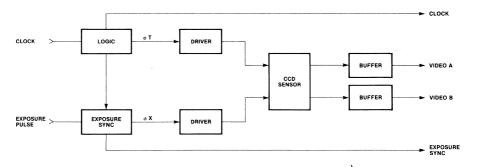

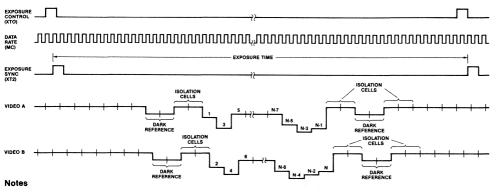

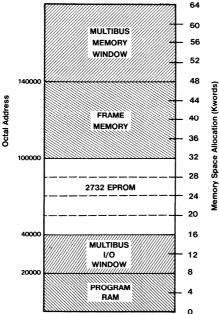

The boards, Figure 1, are 4 1/2 by 5 inches. A socket for installation of the charge coupled device line scan sensor is mounted centrally on the back (wiring) side of the card. The user can readily mount a lens in front of the sensor if required for his study. Board I/0 connections are made through a 22 position double readout edge card connector with .156 inch center-to-center finger spacings. The edge connector is compatible with a TRW/CINCH type 50-44B-10 or equivalent.